#### Subistema de Memoria

#### Subsistema de Memoria

Alejandro Furfaro

12 de octubre de 2020

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

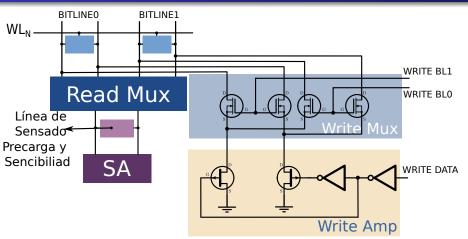

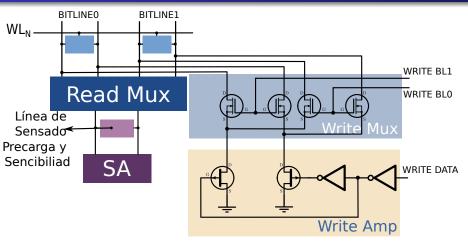

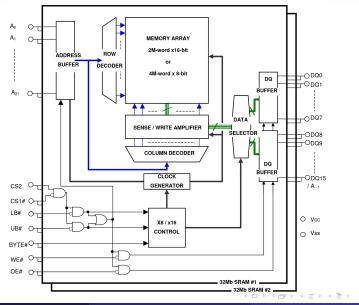

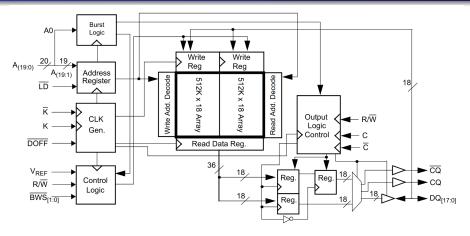

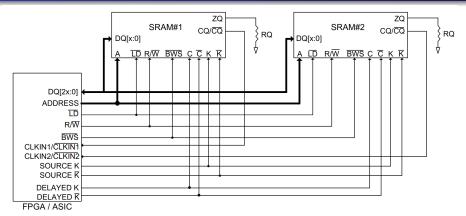

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

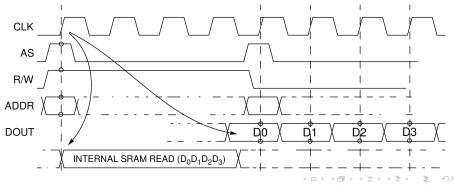

- Timing Conexión física

- Tópicos avanzados de implementación

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

Richard Sites, arquitecto senior de computadores en Digital Equipment Corporation (DEC), uno de los líderes del desarrollo del procesador Alfa, publicó en 1996 un reporte con este título provocador, en el prestigioso "Microprocessor Report".

Richard Sites, arquitecto senior de computadores en Digital Equipment Corporation (DEC), uno de los líderes del desarrollo del procesador Alfa, publicó en 1996 un reporte con este título provocador, en el prestigioso "Microprocessor Report".

Explica la estimación de su equipo en DEC al inicio del proyecto Alfa

Richard Sites, arquitecto senior de computadores en Digital Equipment Corporation (DEC), uno de los líderes del desarrollo del procesador Alfa, publicó en 1996 un reporte con este título provocador, en el prestigioso "Microprocessor Report".

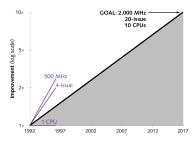

- Explica la estimación de su equipo en DEC al inicio del proyecto Alfa

- Prospección a 25 años (es decir a 2017): performance x1000.

Richard Sites, arquitecto senior de computadores en Digital Equipment Corporation (DEC), uno de los líderes del desarrollo del procesador Alfa, publicó en 1996 un reporte con este título provocador, en el prestigioso "Microprocessor Report".

- Explica la estimación de su equipo en DEC al inicio del proyecto Alfa

- Prospección a 25 años (es decir a 2017): performance x1000.

- Frecuencia de clock x10, # de instrucciones enviadas a ejecución por ciclo de clock x10, y # de cores x10

En 1992 se lanza el procesador Alfa 21064, con una CPU@200Mhz, y superescalar de dos vías (envía dos instrucciones a ejecutar por ciclo de clock).

- En 1992 se lanza el procesador Alfa 21064, con una CPU@200Mhz, y superescalar de dos vías (envía dos instrucciones a ejecutar por ciclo de clock).

- Según la prospección, estas tres magnitudes cuatro años después deberían estar en promedio en x1.45.

- En 1992 se lanza el procesador Alfa 21064, con una CPU@200Mhz, y superescalar de dos vías (envía dos instrucciones a ejecutar por ciclo de clock).

- Según la prospección, estas tres magnitudes cuatro años después deberían estar en promedio en x1.45.

- En 1996 año del artículo, Sites mostró que los pronósticos de estas tres magnitudes fueron conservadores.

- En 1992 se lanza el procesador Alfa 21064, con una CPU@200Mhz, y superescalar de dos vías (envía dos instrucciones a ejecutar por ciclo de clock).

- Según la prospección, estas tres magnitudes cuatro años después deberían estar en promedio en x1.45.

- En 1996 año del artículo, Sites mostró que los pronósticos de estas tres magnitudes fueron conservadores.

- El Alfa 21164 tenía 1 CPU@500Mhz y enviaba 4 instrucciones a ejecución con su superescalar de 4 vías.

- En 1992 se lanza el procesador Alfa 21064, con una CPU@200Mhz, y superescalar de dos vías (envía dos instrucciones a ejecutar por ciclo de clock).

- Según la prospección, estas tres magnitudes cuatro años después deberían estar en promedio en x1.45.

- En 1996 año del artículo, Sites mostró que los pronósticos de estas tres magnitudes fueron conservadores.

- El Alfa 21164 tenía 1 CPU@500Mhz y enviaba 4 instrucciones a ejecución con su superescalar de 4 vías.

- La frecuencia incrementó x2.5, la cantidad de instrucciones enviadas x2 y solo la cantidad de CPUs quedó atrás.

- En 1992 se lanza el procesador Alfa 21064, con una CPU@200Mhz, y superescalar de dos vías (envía dos instrucciones a ejecutar por ciclo de clock).

- Según la prospección, estas tres magnitudes cuatro años después deberían estar en promedio en x1.45.

- En 1996 año del artículo, Sites mostró que los pronósticos de estas tres magnitudes fueron conservadores.

- El Alfa 21164 tenía 1 CPU@500Mhz y enviaba 4 instrucciones a ejecución con su superescalar de 4 vías.

- La frecuencia incrementó x2.5, la cantidad de instrucciones enviadas x2 y solo la cantidad de CPUs quedó atrás.

- Si miramos la prospección a 2017, de las tres magnitudes por separado el pronóstico tenía mucho sentido.

# Perdón...¿Y la performance?

# Perdón...¿Y la performance?

Esa es otra historia...

# Perdón...¿Y la performance?

- Esa es otra historia...

- Un benchmark con bases de datos utilizando TPC-C (Transaction Processing Performance Council.), ejecutados en un procesador Alfa 21164@400Mhz, y un Pentium-Pro@200Mhz, indicó que entregaban un resultado cada 4.2, y 4.5 ciclos de clock respectivamente.

# Perdón...; Y la performance?

- Esa es otra historia...

- Un benchmark con bases de datos utilizando TPC-C (Transaction Processing Performance Council.), ejecutados en un procesador Alfa 21164@400Mhz, y un Pentium-Pro@200Mhz, indicó que entregaban un resultado cada 4.2, y 4.5 ciclos de clock respectivamente.

- Dicho de otro modo, están tres ciclos de clock esperando a la memoria.

# ¿Conclusión?

## ¿Conclusión?

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

Capaces de retener la información almacenada cuando se les desconecta la alimentación.

- Capaces de retener la información almacenada cuando se les desconecta la alimentación.

- Han evolucionado tecnológicamente pasando por múltiples modelos, partiendo de la grabación en fábrica, paulatinamente permitieron su modificación offline, y actualmente, son modificables en tiempo real.

Las viejas memorias denominadas ROM (por Read Only Memory), son las primeras implementaciones. Debían ser grabadas por el fabricante del chip, y no eran modificables.

- Las viejas memorias denominadas *ROM* (por Read Only Memory), son las primeras implementaciones. Debían ser grabadas por el fabricante del chip, y no eran modificables.

- Componentes programables solo una vez (OTPROM), programables y borrables con luz ultravioleta de una determinada longitud de onda (EPROM), etc.

- Las viejas memorias denominadas ROM (por Read Only Memory), son las primeras implementaciones. Debían ser grabadas por el fabricante del chip, y no eran modificables.

- Componentes programables solo una vez (OTPROM), programables y borrables con luz ultravioleta de una determinada longitud de onda (EPROM), etc.

- Las actuales memorias No volátiles denominadas flash por su tecnología de origen, pueden ser grabadas "on the fly"por algoritmos de escritura. Su ejemplo mas habitual son los discos de estado sólido de los equipos portátiles modernos, o las tarjetas SD en los sistemas embedded.

Conocidas como RAM (Random Access Memory), se caracterizan por que una vez interrumpida la alimentación eléctrica, la información que almacenaban se pierde.

- Conocidas como RAM (Random Access Memory), se caracterizan por que una vez interrumpida la alimentación eléctrica, la información que almacenaban se pierde.

- Sin embargo estas memorias pueden almacenar mayores cantidades de información y modificarla en tiempo real a gran velocidad en comparación con las No Volátiles.

- Conocidas como RAM (Random Access Memory), se caracterizan por que una vez interrumpida la alimentación eléctrica, la información que almacenaban se pierde.

- Sin embargo estas memorias pueden almacenar mayores cantidades de información y modificarla en tiempo real a gran velocidad en comparación con las No Volátiles.

- Se clasifican de acuerdo con la tecnología y su diseño interno en dinámicas (*DRAM*)y estáticas (*SRAM*).

La memoria no volátil se usa fundamentalmente para almacenar el programa de arranque de cualquier sistema. Le seguimos diciendo ROM, mas por costumbre que por corrección técnica.

- La memoria no volátil se usa fundamentalmente para almacenar el programa de arranque de cualquier sistema. Le seguimos diciendo ROM, mas por costumbre que por corrección técnica.

- Se conectan en un espacio de direcciones determinado por el propio microprocesador de acuerdo a la dirección en la que éste irá a buscar la primer instrucción luego de encender el equipo.

- La memoria no volátil se usa fundamentalmente para almacenar el programa de arranque de cualquier sistema. Le seguimos diciendo ROM, mas por costumbre que por corrección técnica.

- Se conectan en un espacio de direcciones determinado por el propio microprocesador de acuerdo a la dirección en la que éste irá a buscar la primer instrucción luego de encender el equipo.

- El resto es RAM y allí el sistema copia incluso buena parte del código de arranque para que se ejecute mas rápido ya que las memorias volátiles tienen menor tiempo de acceso, (menos ciclos de clock para acceder al contenido de una dirección).

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

• El sueño: tener un sistema de Memoria de una sola tecnología y sin jerarquía. Diseño simple, costo moderado. Fin.

- El sueño: tener un sistema de Memoria de una sola tecnología y sin jerarquía. Diseño simple, costo moderado. Fin.

- La realidad: Solo en sistemas triviales basados en Microcontroladores sencillos para actividades de control rudimentarias.

- El sueño: tener un sistema de Memoria de una sola tecnología y sin jerarquía. Diseño simple, costo moderado. Fin.

- La realidad: Solo en sistemas triviales basados en Microcontroladores sencillos para actividades de control rudimentarias.

- En un sistema de cómputo un poco mas sofisticado no hay alternativas. Necesitamos mirar la memoria como un subsistema.

- El sueño: tener un sistema de Memoria de una sola tecnología y sin jerarquía. Diseño simple, costo moderado. Fin.

- La realidad: Solo en sistemas triviales basados en Microcontroladores sencillos para actividades de control rudimentarias.

- En un sistema de cómputo un poco mas sofisticado no hay alternativas. Necesitamos mirar la memoria como un subsistema.

- A punto tal que es mas importante el diseño de este subsistema que el de la propia CPU.

- El sueño: tener un sistema de Memoria de una sola tecnología y sin jerarquía. Diseño simple, costo moderado. Fin.

- La realidad: Solo en sistemas triviales basados en Microcontroladores sencillos para actividades de control rudimentarias.

- En un sistema de cómputo un poco mas sofisticado no hay alternativas. Necesitamos mirar la memoria como un subsistema.

- A punto tal que es mas importante el diseño de este subsistema que el de la propia CPU.

- Con los avances de las últimas dos décadas en materia de miniaturización, la interacción entre las diferentes jerarquías no es trivial y afloraron como parte de la problemática del diseño de memoria problemas relacionados con ésta interacción que hasta este siglo tenían mínima influencia. Ejemplo: integridad de señal entre diferentes tipos de memoria y la CPU por ejemplo.

Gran capacidad de almacenamiento

- Gran capacidad de almacenamiento

- Tiempo de acceso mínimo

- Gran capacidad de almacenamiento

- Tiempo de acceso mínimo

- No volatilidad para recuperar los datos un cuando se apague el equipo

- Gran capacidad de almacenamiento

- Tiempo de acceso mínimo

- No volatilidad para recuperar los datos un cuando se apague el equipo

- Y por supuesto no puede faltar en ninguna lista aspiracional: Bajo costo

- Gran capacidad de almacenamiento

- Tiempo de acceso mínimo

- No volatilidad para recuperar los datos un cuando se apague el equipo

- Y por supuesto no puede faltar en ninguna lista aspiracional: Bajo costo

Es una frazada demasiado corta!. Imposible de conseguir con una sola tecnología. De esto deriva la necesidad de construir una jerarquía de memoria.

• Los procesadores mas modernos construidos con tecnología de 14 nm logran leer datos e instrucciones a casi 1.2 Tbps.

- Los procesadores mas modernos construidos con tecnología de 14 nm logran leer datos e instrucciones a casi 1.2 Tbps.

- El costo por bit de la memoria de un equipo de 16GiB de capacidad es en todo concepto inferior a los u\$s 100.

- Los procesadores mas modernos construidos con tecnología de 14 nm logran leer datos e instrucciones a casi 1.2 Tbps.

- El costo por bit de la memoria de un equipo de 16GiB de capacidad es en todo concepto inferior a los u\$s 100.

- El principio rector de la jerarquía de memoria se conoce como localidad de referencia.

- Los procesadores mas modernos construidos con tecnología de 14 nm logran leer datos e instrucciones a casi 1.2 Tbps.

- El costo por bit de la memoria de un equipo de 16GiB de capacidad es en todo concepto inferior a los u\$s 100.

- El principio rector de la jerarquía de memoria se conoce como localidad de referencia.

- Se basa en dos trabajos de investigación de intercambio de bloques de memoria y storage cuando se desarrollaron los algoritmos para manejo de memoria virtual.

- Los procesadores mas modernos construidos con tecnología de 14 nm logran leer datos e instrucciones a casi 1.2 Tbps.

- El costo por bit de la memoria de un equipo de 16GiB de capacidad es en todo concepto inferior a los u\$s 100.

- El principio rector de la jerarquía de memoria se conoce como localidad de referencia.

- Se basa en dos trabajos de investigación de intercambio de bloques de memoria y storage cuando se desarrollaron los algoritmos para manejo de memoria virtual.

- En 1966 L. A. Belady, publicó en IBM System Journal un estudio muy comprensivo y esclarecedor acerca del funcionamiento real del acceso a memoria de un computador.

- Los procesadores mas modernos construidos con tecnología de 14 nm logran leer datos e instrucciones a casi 1.2 Tbps.

- El costo por bit de la memoria de un equipo de 16GiB de capacidad es en todo concepto inferior a los u\$s 100.

- El principio rector de la jerarquía de memoria se conoce como localidad de referencia.

- Se basa en dos trabajos de investigación de intercambio de bloques de memoria y storage cuando se desarrollaron los algoritmos para manejo de memoria virtual.

- En 1966 L. A. Belady, publicó en IBM System Journal un estudio muy comprensivo y esclarecedor acerca del funcionamiento real del acceso a memoria de un computador.

- En pocas palabras, sus conclusiones fueron: el acceso a memoria no es tan aleatorio como el "Random Access Memory"lo sugiere, sino que por el contrario es bastante predecible.

#### Observación empírica

Si tomamos cualquier programa medianamente bien escrito, que respete nimiamente las buenas prácticas de programación, veremos que los acceso a memoria se restringen a un intervalo continuo de direcciones de memoria durante una cantidad de tiempo significativa.

### Localidad temporal

Se refiere a un patrón de acceso a las mismas direcciones de memoria en un intervalo temporal finito y acotado.

Las direcciones de memoria que la CPU está utilizando actualmente tienen una probabilidad muy alta de seguir siendo accedidas en los próximos ciclos de memoria.

La probabilidad de iniciar un ciclo de memoria hacia direcciones que no están siendo utilizadas, en cambio, es muy baja.

#### Localidad espacial

Se refiere al espacio de direcciones que utiliza una CPU en un intervalo temporal finito y acotado.

La probabilidad que la CPU utilice direcciones vecinas a la del objeto que está direccionando actualmente es muy alta.

Contrariamente es muy poco probable que utilice direcciones no vecinas.

```

for (i = 0 ; i < 256 ; i++ )

suma = 0.0 f;

for (j = 0 ; (j <= i && j < 256) ; j++)

suma += v0[i-j] * v1[j];

fAux[i] = suma;

}

```

```

for (i = 0 ; i < 256 ; i++)

suma = 0.0 f;

for (j = 0 ; (j <= i && j < 256) ; j++)

suma += v0[i-j] * v1[j];

fAux[i] = suma;

}

```

Las variables i, j, suma, se utilizan muy a menudo. Son claro ejemplo del principio de vecindad temporal. Las mismas direcciones se emplean con una frecuencia de uso alta.

```

for (i = 0 ; i < 256 ; i++ )

{

suma = 0.0 f;

for (j = 0 ; (j <= i && j < 256) ; j++)

suma += v0[i-j] * v1[j];

fAux[i] = suma;

}

```

- Las variables i, j, suma, se utilizan muy a menudo. Son claro ejemplo del principio de vecindad temporal. Las mismas direcciones se emplean con una frecuencia de uso alta.

- El espacio de direcciones del código verifica el principio de localidad espacial. La probabilidad de acceso a direcciones de ese espacio es alta mientras estemos dentro de ese loop y no haya conmutación de tareas.

- Las variables i, j, suma, se utilizan muy a menudo. Son claro ejemplo del principio de vecindad temporal. Las mismas direcciones se emplean con una frecuencia de uso alta.

- El espacio de direcciones del código verifica el principio de localidad espacial. La probabilidad de acceso a direcciones de ese espacio es alta mientras estemos dentro de ese loop y no haya conmutación de tareas.

- Idea: Si logramos que este código y las variables estén en una memoria rápida cuando el procesador los necesite, su tiempo de acceso será mínimo (óptimo) para ejecutar la convolución.

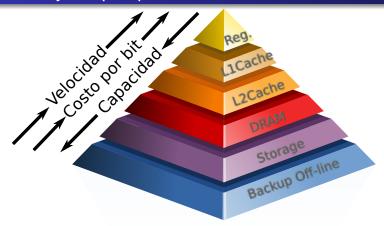

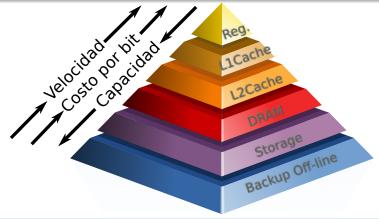

## Memoria: jerarquía piramidal

### Memoria: jerarquía piramidal

La jerarquía piramidal plantea que si los datos y el código que el procesador utiliza están (casi) siempre cerca del vértice (es decir, en las memorias mas rápidas), el sistema se comporta de manera óptima.

### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- 3 Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

$$CPI = \frac{TEC}{TIC} \tag{1}$$

**CPI** = Cycles per Instruction; **TEC** = Total execution cycles; **TIC** = Total user-level Instructions Committed

$$CPI = \frac{TEC}{TIC} \tag{1}$$

**CPI** = Cycles per Instruction; **TEC** = Total execution cycles; **TIC** = Total user-level Instructions Committed

$$MemSys\_CPI\_Ovrh = RealCPI - TeoricCPI$$

(2)

**MemSys\_CPI\_Ovrh** = Memory System CPI Overhead; **Real CPI** = CPI Real (el que se mide); **TeoricCPI** = CPI considerando Memoria Ideal.

$$CPI = \frac{TEC}{TIC} \tag{1}$$

**CPI** = Cycles per Instruction; **TEC** = Total execution cycles; **TIC** = Total user-level Instructions Committed

$$MemSys\_CPI\_Ovrh = RealCPI - TeoricCPI$$

(2)

**MemSys\_CPI\_Ovrh** = Memory System CPI Overhead; **Real CPI** = CPI Real (el que se mide); **TeoricCPI** = CPI considerando Memoria Ideal.

$$MCPI = \frac{TMC}{TIC}$$

(3)

**MCPI** = Memory Cycles Per Instruction; **RealTMC** = Ciclos de clock totales insumidos por la memoria; **TIC** = Total user-level Instructions Committed.

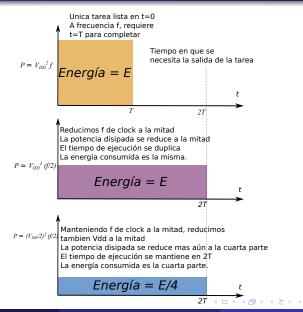

### Energía y Potencia

## Energía y Potencia

En Física, Energía consumida es el trabajo efectuado para una tarea.

- En Física, Energía consumida es el trabajo efectuado para una tarea.

- Aplicado a un sistema de cómputo, la Energía consumida es la medida de cuanta carga de batería consume un algoritmo.

- En Física, Energía consumida es el trabajo efectuado para una tarea.

- Aplicado a un sistema de cómputo, la Energía consumida es la medida de cuanta carga de batería consume un algoritmo.

- Sin embargo en general los Microprocesadores y las memorias, especifican Potencia instantánea. (Watts)

- En Física, Energía consumida es el trabajo efectuado para una tarea.

- Aplicado a un sistema de cómputo, la Energía consumida es la medida de cuanta carga de batería consume un algoritmo.

- Sin embargo en general los Microprocesadores y las memorias, especifican Potencia instantánea. (Watts)

- En los dispositivos CMOS se especifica el promedio de los valores de Potencia instantánea en el período de conmutación del transistor CMOS (corte a saturación o visceversa).

- En Física, Energía consumida es el trabajo efectuado para una tarea.

- Aplicado a un sistema de cómputo, la Energía consumida es la medida de cuanta carga de batería consume un algoritmo.

- Sin embargo en general los Microprocesadores y las memorias, especifican Potencia instantánea. (Watts)

- En los dispositivos CMOS se especifica el promedio de los valores de Potencia instantánea en el período de conmutación del transistor CMOS (corte a saturación o visceversa).

$$P_{avg} = (P_{dynamic} + P_{static}) \approx C_{tot} V_{dd}^2 f + I_{leak} V_{dd}$$

(4)

$P_{avg}$  = Potencia promedio disipada;  $C_{tot}$  = Capacidad total de carga del CMOS;  $V_{dd}$  = Tensión de alimentación; f = Frecuencia de conmutación (clock); e  $I_{leak}$  = Corriente de pérdida (No me digas que te creíste que un CMOS al corte no conduce corriente en la malla de salida... ¡Dale!)

La corriente de pérdida I<sub>leak</sub>, es muy baja pero a partir de las tecnologías de 45 a 30 nm dejó de disminuir conforme se miniaturiza un transistor. Otra mala noticia para el tramo final de la Ley de Moore: leakage pasó a ser un "big issue".

- La corriente de pérdida I<sub>leak</sub>, es muy baja pero a partir de las tecnologías de 45 a 30 nm dejó de disminuir conforme se miniaturiza un transistor. Otra mala noticia para el tramo final de la Ley de Moore: leakage pasó a ser un "big issue".

- La Energía está directamente relacionada con la potencia a través del tiempo. De hecho, la potencia media en un intervalo de tiempo es la relación entre la Energía y la duración del intervalo.

- La corriente de pérdida I<sub>leak</sub>, es muy baja pero a partir de las tecnologías de 45 a 30 nm dejó de disminuir conforme se miniaturiza un transistor. Otra mala noticia para el tramo final de la Ley de Moore: leakage pasó a ser un "big issue".

- La Energía está directamente relacionada con la potencia a través del tiempo. De hecho, la potencia media en un intervalo de tiempo es la relación entre la Energía y la duración del intervalo.

- En un intervalo T, la cantidad de Joules consumidos es:

- La corriente de pérdida I<sub>leak</sub>, es muy baja pero a partir de las tecnologías de 45 a 30 nm dejó de disminuir conforme se miniaturiza un transistor. Otra mala noticia para el tramo final de la Ley de Moore: leakage pasó a ser un "big issue".

- La Energía está directamente relacionada con la potencia a través del tiempo. De hecho, la potencia media en un intervalo de tiempo es la relación entre la Energía y la duración del intervalo.

- En un intervalo T, la cantidad de Joules consumidos es:

$$E = P_{avg}.T \approx C_{tot}V_{dd}^2N + I_{leak}V_{dd}.T$$

(5)

**N** = Cantidad de eventos de switching ocurridos en el intervalo T.

- La corriente de pérdida I<sub>leak</sub>, es muy baja pero a partir de las tecnologías de 45 a 30 nm dejó de disminuir conforme se miniaturiza un transistor. Otra mala noticia para el tramo final de la Ley de Moore: leakage pasó a ser un "big issue".

- La Energía está directamente relacionada con la potencia a través del tiempo. De hecho, la potencia media en un intervalo de tiempo es la relación entre la Energía y la duración del intervalo.

- En un intervalo T, la cantidad de Joules consumidos es:

$$E = P_{avg}.T \approx C_{tot}V_{dd}^2N + I_{leak}V_{dd}.T$$

(5)

- **N** = Cantidad de eventos de switching ocurridos en el intervalo T.

- Una primer conclusión es que la energía consumida por un algoritmo (la medida del trabajo que realiza el computador) no depende de la frecuencia de clock.

Cuando nos referimos al consumo, lo correcto es hablar de Joules, es decir, Energía. Esto es duración de batería, o KWh en la factura del servicio de electricidad. Sin embargo coloquialmente se suele hablar de energía cuando se miden los Watts instantáneos de un chip. Esto no es correcto.

- Cuando nos referimos al consumo, lo correcto es hablar de Joules, es decir, Energía. Esto es duración de batería, o KWh en la factura del servicio de electricidad. Sin embargo coloquialmente se suele hablar de energía cuando se miden los Watts instantáneos de un chip. Esto no es correcto.

- Típico anuncio de marketing: "Nuestra nueva familia de procesadores "low power" mejora a la línea anterior en un factor de 2".

- Cuando nos referimos al consumo, lo correcto es hablar de Joules, es decir, Energía. Esto es duración de batería, o KWh en la factura del servicio de electricidad. Sin embargo coloquialmente se suele hablar de energía cuando se miden los Watts instantáneos de un chip. Esto no es correcto.

- Típico anuncio de marketing: "Nuestra nueva familia de procesadores "low power" mejora a la línea anterior en un factor de 2".

- Bien. Esto puede lograrse simplemente subclockeando a la mitad de frecuencia, reduciendo así a la mitad la potencia disipada.

- Cuando nos referimos al consumo, lo correcto es hablar de Joules, es decir, Energía. Esto es duración de batería, o KWh en la factura del servicio de electricidad. Sin embargo coloquialmente se suele hablar de energía cuando se miden los Watts instantáneos de un chip. Esto no es correcto.

- Típico anuncio de marketing: "Nuestra nueva familia de procesadores "low power" mejora a la línea anterior en un factor de 2".

- Bien. Esto puede lograrse simplemente subclockeando a la mitad de frecuencia, reduciendo así a la mitad la potencia disipada.

- Sin embargo, la potencia puede perfectamente definirse como la velocidad a la que se consume la energía.

- Cuando nos referimos al consumo, lo correcto es hablar de Joules, es decir, Energía. Esto es duración de batería, o KWh en la factura del servicio de electricidad. Sin embargo coloquialmente se suele hablar de energía cuando se miden los Watts instantáneos de un chip. Esto no es correcto.

- Típico anuncio de marketing: "Nuestra nueva familia de procesadores "low power" mejora a la línea anterior en un factor de 2".

- Bien. Esto puede lograrse simplemente subclockeando a la mitad de frecuencia, reduciendo así a la mitad la potencia disipada.

- Sin embargo, la potencia puede perfectamente definirse como la velocidad a la que se consume la energía.

- Subclockear solo disminuye la velocidad con que se descarga la batería. El trabajo realizado en Joules para un dado algoritmo no cambia. Tardará el doble en hacerlo.

Considerando lo dicho en el slide anterior, las métricas que valen la pena y suelen encontrarse son las siguientes:

- Considerando lo dicho en el slide anterior, las métricas que valen la pena y suelen encontrarse son las siguientes:

- Energy-Delay Product

${\it Energy-DelayProduct} = {\it EnergiaRequeridaPorLaTarea}. TiempoRequeridoPorLaTarea$

(6)

- Considerando lo dicho en el slide anterior, las métricas que valen la pena y suelen encontrarse son las siguientes:

- Energy-Delay Product

Energy — DelayProduct = EnergiaRequeridaPorLaTarea. TiempoRequeridoPorLaTarea (6)

• Power-Delay Product

Power-DelayProduct = PotenciaConsumidaPorLaTarea. Tiempo Requerido PorLaTarea

-(7)

- Considerando lo dicho en el slide anterior, las métricas que valen la pena y suelen encontrarse son las siguientes:

- Energy-Delay Product

Energy – DelayProduct = EnergiaRequeridaPorLaTarea. TiempoRequeridoPorLaTarea (6)

• Power-Delay Product

Power – DelayProduct = PotenciaConsumidaPorLaTarea. TiempoRequeridoPorLaTarea

MIPS per watt

MIPSperWatt = PerformanceBenchmarckEnMIPS PotenciaPromedioDisipadaPorLaTarea (8)

• El costo de producir una memoria involucra una serie de factores:

- El costo de producir una memoria involucra una serie de factores:

- El costo de producir un chip VLSI es proporcional al tamaño del die de Si.

- El costo de producir una memoria involucra una serie de factores:

- El costo de producir un chip VLSI es proporcional al tamaño del die de Si.

- El packaging también es una componente. El pinout y la tecnología de montaje seleccionados inciden en el costo de la memoria

- El costo de producir una memoria involucra una serie de factores:

- El costo de producir un chip VLSI es proporcional al tamaño del die de Si.

- El packaging también es una componente. El pinout y la tecnología de montaje seleccionados inciden en el costo de la memoria

- Complejidad de Diseño. Involucra, la cantidad de líneas de código HDL, a mayor cantidad mas complejo es el diseño síntesis y testing. Además requiere mayor cantidad de transistores.

- El costo de producir una memoria involucra una serie de factores:

- El costo de producir un chip VLSI es proporcional al tamaño del die de Si.

- El packaging también es una componente. El pinout y la tecnología de montaje seleccionados inciden en el costo de la memoria

- Complejidad de Diseño. Involucra, la cantidad de líneas de código HDL, a mayor cantidad mas complejo es el diseño síntesis y testing. Además requiere mayor cantidad de transistores.

- El clock de trabajo claramente incide en la complejidad de diseño de los montajes

- El costo de producir una memoria involucra una serie de factores:

- El costo de producir un chip VLSI es proporcional al tamaño del die de Si.

- El packaging también es una componente. El pinout y la tecnología de montaje seleccionados inciden en el costo de la memoria

- Complejidad de Diseño. Involucra, la cantidad de líneas de código HDL, a mayor cantidad mas complejo es el diseño síntesis y testing. Además requiere mayor cantidad de transistores.

- El clock de trabajo claramente incide en la complejidad de diseño de los montajes

- Las métricas habituales son: Costo por Bit, por byte, por KioBibyte, etc., Área de Die por bit de almacenamiento (dá una idea de la densidad o capacidad del dispositivo), ancho de banda por pin de encapsulado, entre otros.

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

Un sistema jerárquico de memoria, tiene por objetivo que el comportamiento el sistema se aproxime al del componente mas rápido, logrando el costo por bit mas bajo posible, y la mayor eficiencia de energía posible.

- Un sistema jerárquico de memoria, tiene por objetivo que el comportamiento el sistema se aproxime al del componente mas rápido, logrando el costo por bit mas bajo posible, y la mayor eficiencia de energía posible.

- Independientemente de la escala del sistema bajo análisis, siempre vamos a poder identificar la presencia de diferentes niveles jerárquicos.

- Un sistema jerárquico de memoria, tiene por objetivo que el comportamiento el sistema se aproxime al del componente mas rápido, logrando el costo por bit mas bajo posible, y la mayor eficiencia de energía posible.

- Independientemente de la escala del sistema bajo análisis, siempre vamos a poder identificar la presencia de diferentes niveles jerárquicos.

- Al menos dos niveles en los microcontroladores mas modestos.

- Un sistema jerárquico de memoria, tiene por objetivo que el comportamiento el sistema se aproxime al del componente mas rápido, logrando el costo por bit mas bajo posible, y la mayor eficiencia de energía posible.

- Independientemente de la escala del sistema bajo análisis, siempre vamos a poder identificar la presencia de diferentes niveles jerárquicos.

- Al menos dos niveles en los microcontroladores mas modestos.

- A medida que aumentamos la escala del procesador base, la cantidad de niveles aumenta consistentemente

- Un sistema jerárquico de memoria, tiene por objetivo que el comportamiento el sistema se aproxime al del componente mas rápido, logrando el costo por bit mas bajo posible, y la mayor eficiencia de energía posible.

- Independientemente de la escala del sistema bajo análisis, siempre vamos a poder identificar la presencia de diferentes niveles jerárquicos.

- Al menos dos niveles en los microcontroladores mas modestos.

- A medida que aumentamos la escala del procesador base, la cantidad de niveles aumenta consistentemente

- Veamos:

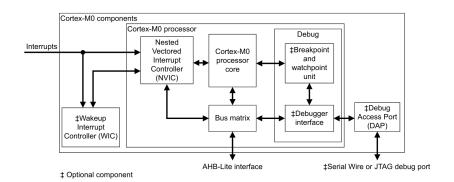

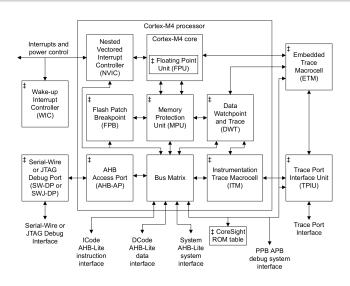

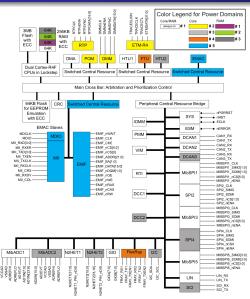

#### Caso 1: Cortex M0

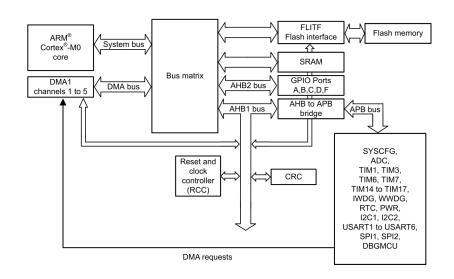

### Caso 1: STM32F030x

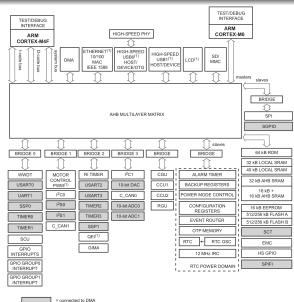

### Caso 2: Cortex M4

### Caso 2: LPC433x

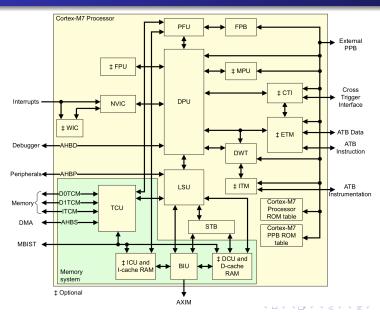

#### Caso 3: CortexM7

#### Caso 3: iMX RT 1050

| System Control                  | CPU Platform                                                                      |                        |  | Connectivity                       |

|---------------------------------|-----------------------------------------------------------------------------------|------------------------|--|------------------------------------|

| Secure JTAG                     | Arm Cortex-M7                                                                     |                        |  | eMMC 4.5 / SD 3.0 x2               |

| PLL / OSC                       | 32 KB I-cache                                                                     | 32 KB D-cache          |  | UART x8                            |

| RTC and Reset                   | FPU MPU                                                                           | NVIC                   |  | 0/111 X0                           |

| Enhanced DMA                    |                                                                                   | 12 KB TCM              |  | 8 x 8 Keypad                       |

| IOMUX                           | Up to 5.                                                                          | 12 KB ICM              |  | 12C x4                             |

| GP Timer x6                     |                                                                                   |                        |  |                                    |

| Quadrature ENC x4               | Multimedia                                                                        |                        |  | SPI x4                             |

| QuadTimer<br>(4-Channel) x4     | 8 / 16 / 24-bit Parallel CSI                                                      |                        |  | GPIO                               |

| FlexPWM<br>(8-Channel) x4       | 24-bit Parallel LCD                                                               |                        |  | 12S / SAI x3                       |

| Watch Dog x4                    | PXP                                                                               |                        |  | S/PDIF Tx / Rx                     |

| Internal Memory                 | 2D Graphics Acceleration<br>Resize, CSC, Overlay, Rotation                        |                        |  | FlexCAN x2                         |

| 512 KB OCRAM<br>shared with TCM | External Memory FlexSPI (dual-channel QuadSPI NAND and NOR, Octal Flash, and RAM) |                        |  | JSB 2.0 OTG with PHY x2            |

| 96 KB ROM                       |                                                                                   |                        |  | 10 / 100 ENET<br>with IEEE 1588 x1 |

| Power Management  DCDC          | External Memory Controller<br>8-bit / 16-bit SDRAM                                |                        |  | ADC                                |

| LDO                             |                                                                                   | l nor flash<br>D flash |  | ADC x2 (20-Channel)                |

| Temp Monitor                    | Р                                                                                 | SRAM                   |  | ACMP x4                            |

| Security                        |                                                                                   |                        |  |                                    |

| Ciphers and RNG                 | Secure RTC                                                                        | eFuse                  |  | нав                                |

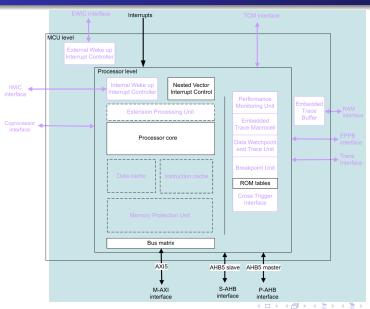

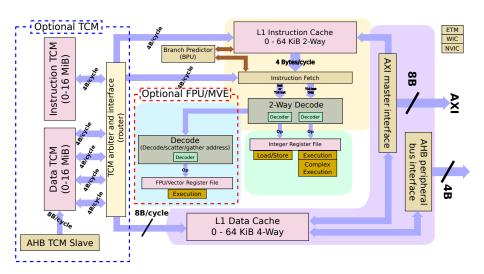

#### Caso 4: Cortex M55

### Caso 4: Cortex M55

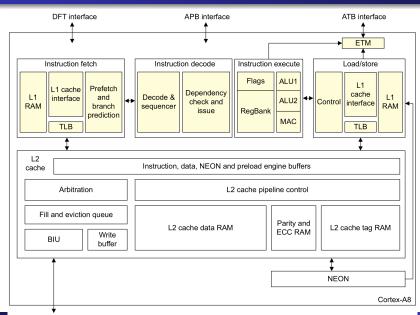

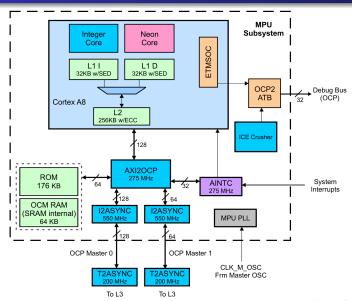

#### Caso 5: Cortex A8

#### Caso 5: Sitara 335x

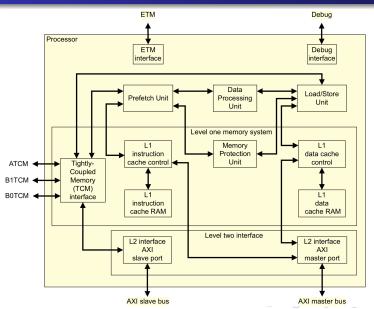

#### Caso 6: Cortex R4

#### Caso 6: TMS570

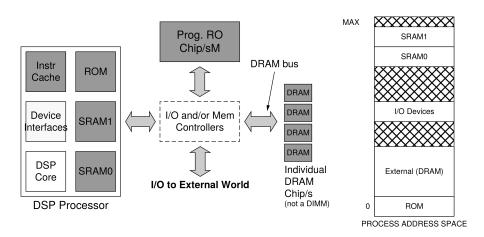

### Caso 7: Un DSP embedded no ARM

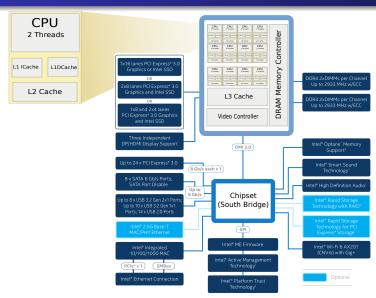

#### Caso 8: Fuerza bruta

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

La potencia dispada en circuitos basados en transistores CMOS proviene de dos factores

- La potencia dispada en circuitos basados en transistores CMOS proviene de dos factores

- Potencia estática (leakage power): Proviene del hecho que un transistor CMOS cuando está en estado de corte no está completamente "apagado".

- La potencia dispada en circuitos basados en transistores CMOS proviene de dos factores

- Potencia estática (leakage power): Proviene del hecho que un transistor CMOS cuando está en estado de corte no está completamente "apagado".

- ✓ Potencia dinámica: Resultado de conmutar a una carga capacitiva en la malla de salida entre dos estados de tensión.

- La potencia dispada en circuitos basados en transistores CMOS proviene de dos factores

- Potencia estática (leakage power): Proviene del hecho que un transistor CMOS cuando está en estado de corte no está completamente "apagado".

- ✓ Potencia dinámica: Resultado de conmutar a una carga capacitiva en la malla de salida entre dos estados de tensión.

- La Potencia dinámica depende de la actividad de conmutación del circuito. Es decir de la frecuencia con que conmute. Si no cambia el valor de tensión en al salida del CMOS, no hay conmutación, y no se disipa potencia.

- La potencia dispada en circuitos basados en transistores CMOS proviene de dos factores

- Potencia estática (leakage power): Proviene del hecho que un transistor CMOS cuando está en estado de corte no está completamente "apagado".

- ✓ Potencia dinámica: Resultado de conmutar a una carga capacitiva en la malla de salida entre dos estados de tensión.

- La Potencia dinámica depende de la actividad de conmutación del circuito. Es decir de la frecuencia con que conmute. Si no cambia el valor de tensión en al salida del CMOS, no hay conmutación, y no se disipa potencia.

- Por su parte la *Potencia estática* es independiente de la frecuencia, y existe simplemente porque el chip está alimentado.

La tecnología CMOS se destacó por su potencia de leakage prácticamente despreciable. Esa fue la razón de su adopción para transistores de circuitos lógicos.

- La tecnología CMOS se destacó por su potencia de leakage prácticamente despreciable. Esa fue la razón de su adopción para transistores de circuitos lógicos.

- Conforme avanzó la tecnología de integración, el tamaño de los transistores se redujo notablemente (scaling)

- La tecnología CMOS se destacó por su potencia de leakage prácticamente despreciable. Esa fue la razón de su adopción para transistores de circuitos lógicos.

- Conforme avanzó la tecnología de integración, el tamaño de los transistores se redujo notablemente (scaling)

- La Potencia dinámica se reduce linealmente con el tamaño del gate del transistor CMOS.

- La tecnología CMOS se destacó por su potencia de leakage prácticamente despreciable. Esa fue la razón de su adopción para transistores de circuitos lógicos.

- Conforme avanzó la tecnología de integración, el tamaño de los transistores se redujo notablemente (scaling)

- La Potencia dinámica se reduce linealmente con el tamaño del gate del transistor CMOS.

- La potencia de leakage no.

- La tecnología CMOS se destacó por su potencia de leakage prácticamente despreciable. Esa fue la razón de su adopción para transistores de circuitos lógicos.

- Conforme avanzó la tecnología de integración, el tamaño de los transistores se redujo notablemente (scaling)

- La Potencia dinámica se reduce linealmente con el tamaño del gate del transistor CMOS.

- La potencia de leakage no.

- La consecuencia de esta situación es que con el tiempo pasó a ser mas significativa que la potencia dinámica.

- La tecnología CMOS se destacó por su potencia de leakage prácticamente despreciable. Esa fue la razón de su adopción para transistores de circuitos lógicos.

- Conforme avanzó la tecnología de integración, el tamaño de los transistores se redujo notablemente (scaling)

- La Potencia dinámica se reduce linealmente con el tamaño del gate del transistor CMOS

- La potencia de leakage no.

- La consecuencia de esta situación es que con el tiempo pasó a ser mas significativa que la potencia dinámica.

- En 2005 aproximadamente los diseñadores tenían como objetivo de diseño mantener la potencia de leakage en no mas del 25 % de la potencia disipada total.

- La tecnología CMOS se destacó por su potencia de leakage prácticamente despreciable. Esa fue la razón de su adopción para transistores de circuitos lógicos.

- Conforme avanzó la tecnología de integración, el tamaño de los transistores se redujo notablemente (scaling)

- La Potencia dinámica se reduce linealmente con el tamaño del gate del transistor CMOS.

- La potencia de leakage no.

- La consecuencia de esta situación es que con el tiempo pasó a ser mas significativa que la potencia dinámica.

- En 2005 aproximadamente los diseñadores tenían como objetivo de diseño mantener la potencia de leakage en no mas del 25 % de la potencia disipada total.

- Luego de los 30nm a 40nm, la Potencia de leakage ya no disminuye con el scaling.

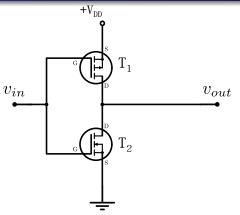

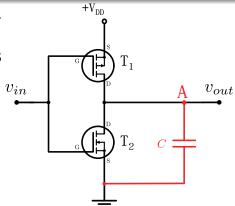

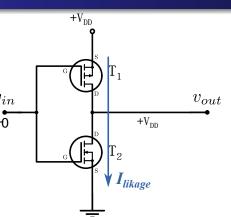

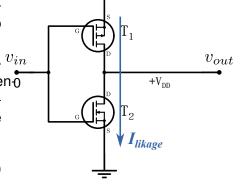

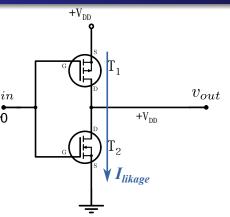

A la derecha un circuito Inversor CMOS

- A la derecha un circuito Inversor CMOS

- Si lo cargamos con otro CMOS la carga es capacitiva.

A la derecha un circuito Inversor CMOS

Si lo cargamos con otro CMOS la carga es capacitiva.

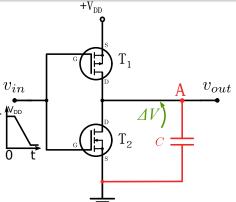

Si en el nodo A se produce una variación de tensión ΔV, se genera una corriente para cargar el capacitor C ΔV Volts, y descargarlo a su valor de tensión original.

A la derecha un circuito Inversor CMOS

Si lo cargamos con otro CMOS la carga es capacitiva.

Si en el nodo A se produce una variación de tensión ΔV, se genera una corriente para cargar el capacitor C ΔV Volts, y descargarlo a su valor de tensión original.

Se genera un flujo de carga igual a C.ΔV desde el Nodo V<sub>DD</sub>,hasta el capacitor y desde este por la malla de descarga.

Finalizado el ciclo carga/descarga el CMOS y el capacitor movieron desde  $V_{DD}$  hasta tierra una cantidad de carga eléctrica igual a  $C.\Delta V$ . Esto significa que han utilizado una cantidad de Energía igual a  $C.\Delta V.V_{DD}$

Y esa Energía es independiente del ciclo de tiempo en el que se realiza el movimiento de carga

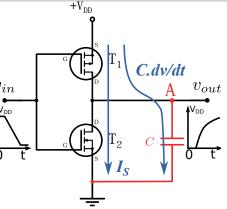

La potencia dinámica promedio de este nodo es la velocidad a la que se consume esta energía, que viene dada por <sup>1</sup>:

$$P_{dyn} = \frac{C.\Delta V. V_{DD}.\alpha}{T},$$

(9)

50/144

Aleiandro Furfaro Subsistema de Memoria 12 de octubre de 2020

<sup>&</sup>lt;sup>1</sup>Chapter 3. Low Power Digital CMOS Design. Chandrakasan & R. W. Brodersen. Publisher: Springer US, Year: 1995

La potencia dinámica promedio de este nodo es la velocidad a la que se consume esta energía, que viene dada por 1:

$$P_{dyn} = \frac{C.\Delta V. V_{DD}.\alpha}{T},$$

(9)

donde T es el período de carga / descarga, es decir, la inversa de la frecuencia de clock, y la razón de actividad  $\alpha$ ,  $0 \le \alpha \le 1$ , es la probabilidad que el nodo conmute, en cuyo caso consumirá energía (si el nodo no conmuta no se consume energía).

Aleiandro Furfaro

<sup>&</sup>lt;sup>1</sup>Chapter 3. Low Power Digital CMOS Design. Chandrakasan & R. W. Brodersen. Publisher: Springer US, Year: 1995

La potencia dinámica promedio de este nodo es la velocidad a la que se consume esta energía, que viene dada por <sup>1</sup>:

$$P_{dyn} = \frac{C.\Delta V. V_{DD}.\alpha}{T},$$

(9)

50/144

donde T es el período de carga / descarga, es decir, la inversa de la frecuencia de clock, y la *razón de actividad*  $\alpha$ ,  $0 \le \alpha \le 1$ , es la probabilidad que el nodo conmute, en cuyo caso consumirá energía (si el nodo no conmuta no se consume energía).

Incluir  $\alpha$  permite estimar el consumo del nodo durante mucho mas que un período de la señal de clock, permitiendo calcular la potencia promedio durante horas enteras de computación, siempre que la *razón de actividad* se mantenga.

Aleiandro Furfaro Subsistema de Memoria 12 de octubre de 2020

<sup>&</sup>lt;sup>1</sup>Chapter 3. Low Power Digital CMOS Design. Chandrakasan & R. W. Brodersen. Publisher: Springer US, Year: 1995

La potencia dinámica promedio de este nodo es la velocidad a la que se consume esta energía, que viene dada por <sup>1</sup>:

$$P_{dyn} = \frac{C.\Delta V. V_{DD}.\alpha}{T},$$

(9)

donde T es el período de carga / descarga, es decir, la inversa de la frecuencia de clock, y la *razón de actividad*  $\alpha$ ,  $0 \le \alpha \le 1$ , es la probabilidad que el nodo conmute, en cuyo caso consumirá energía (si el nodo no conmuta no se consume energía).

Incluir  $\alpha$  permite estimar el consumo del nodo durante mucho mas que un período de la señal de clock, permitiendo calcular la potencia promedio durante horas enteras de computación, siempre que la *razón de actividad* se mantenga.

La suma de la ecuación (9) a lo largo de todos los nodos del chip dá como resultado la **Potencia Dinámica** total.

<sup>&</sup>lt;sup>1</sup>Chapter 3. Low Power Digital CMOS Design. Chandrakasan & R. W. Brodersen. Publisher: Springer US, Year: 1995

De la ecuación (9) surge que si disminuyen la Capacidad de carga, o V<sub>DD</sub>, disminuirá de manera directa la *Potencia Dinámica*.

## Conmutación con carga capacitiva

De la ecuación (9) surge que si disminuyen la Capacidad de carga, o V<sub>DD</sub>, disminuirá de manera directa la **Potencia Dinámica**.

En un circuito lógico la excursión de Tensión  $C.\Delta V$  normalmente es desde un valor muy cercano a 0 Volts hasta V<sub>DD</sub>, de modo que la ecuación (9) se transforma en:

$$P_{dyn} = C.V_{DD}^2.\alpha.f, (10)$$

# Conmutación con carga capacitiva

De la ecuación (9) surge que si disminuyen la Capacidad de carga, o  $V_{DD}$ , disminuirá de manera directa la **Potencia Dinámica**.

En un circuito lógico la excursión de Tensión  $C.\Delta V$  normalmente es desde un valor muy cercano a 0 Volts hasta  $V_{DD}$ , de modo que la ecuación (9) se transforma en:

$$P_{dyn} = C.V_{DD}^2.\alpha.f, (10)$$

Además se verifica empíricamente que la *razón de actividad* en circuitos lógicos es ½, de modo que la ecuación (13) queda:

$$P_{dyn} = \frac{1}{2}.C.V_{DD}^{2}.f,$$

(11)

# Conmutación con carga capacitiva

De la ecuación (9) surge que si disminuyen la Capacidad de carga, o  $V_{DD}$ , disminuirá de manera directa la **Potencia Dinámica**.

En un circuito lógico la excursión de Tensión  $C.\Delta V$  normalmente es desde un valor muy cercano a 0 Volts hasta  $V_{DD}$ , de modo que la ecuación (9) se transforma en:

$$P_{dyn} = C.V_{DD}^2.\alpha.f, (10)$$

Además se verifica empíricamente que la *razón de actividad* en circuitos lógicos es ½, de modo que la ecuación (13) queda:

$$P_{dyn} = \frac{1}{2}.C.V_{DD}^{2}.f,$$

(11)

La ecuación (11) es la que mejor representa la **Potencia Dinámica** en un chip, considerando que es la suma de todos los nodos del chip.

• Como ya se dijo, es la imposibilidad de apagar por completo al transistor CMOS cuando éste está en el estado de corte.

- Como ya se dijo, es la imposibilidad de apagar por completo al transistor CMOS cuando éste está en el estado de corte.

- Así que conduce corriente por debajo del umbral de conducción.

- Como ya se dijo, es la imposibilidad de apagar por completo al transistor CMOS cuando éste está en el estado de corte.

- Así que conduce corriente por debajo del umbral de conducción.

- La compuerta se acopla al canal activo principalmente a través de la capacitancia de óxido de la compuerta.

- Como ya se dijo, es la imposibilidad de apagar por completo al transistor CMOS cuando éste está en el estado de corte.

- Así que conduce corriente por debajo del umbral de conducción.

- La compuerta se acopla al canal activo principalmente a través de la capacitancia de óxido de la compuerta.

- Hay otras capacitancias en un transistor que acoplan la compuerta del CMOS a una suerte de "carga fija" (una carga que no puede moverse) presente en el bloque y no asociada con el flujo de corriente

- Como ya se dijo, es la imposibilidad de apagar por completo al transistor CMOS cuando éste está en el estado de corte.

- Así que conduce corriente por debajo del umbral de conducción.

- La compuerta se acopla al canal activo principalmente a través de la capacitancia de óxido de la compuerta.

- Hay otras capacitancias en un transistor que acoplan la compuerta del CMOS a una suerte de "carga fija" (una carga que no puede moverse) presente en el bloque y no asociada con el flujo de corriente.

- Si estas Capacidades son grandes pueden alterar la polarización de la compuerta cambiando la densidad de carga fija acumulada en el canal impidiendo que este corte.

- Como ya se dijo, es la imposibilidad de apagar por completo al transistor CMOS cuando éste está en el estado de corte.

- Así que conduce corriente por debajo del umbral de conducción.

- La compuerta se acopla al canal activo principalmente a través de la capacitancia de óxido de la compuerta.

- Hay otras capacitancias en un transistor que acoplan la compuerta del CMOS a una suerte de "carga fija" (una carga que no puede moverse) presente en el bloque y no asociada con el flujo de corriente.

- Si estas Capacidades son grandes pueden alterar la polarización de la compuerta cambiando la densidad de carga fija acumulada en el canal impidiendo que este corte.

- Estas capacidades no se reducen con el scaling ya que no dependen de las dimensiones físicas del canal.

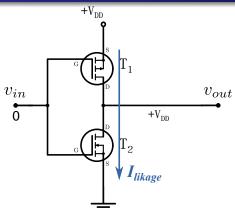

Una vez terminada la conmutación el CMOS queda en un estado estable como el mostrado en la figura de la derecha.

- Una vez terminada la conmutación el CMOS queda en un estado estable como el mostrado en la figura de la derecha.

- La Potencia de leakage es li-<sup>vin</sup> nealmente dependiente de la ten o sión de alimentación, de acuerdo con una expresión bastante simple:

$$P_{stat} = I_{leakage}.V_{DD},$$

(12)

$+V_{DD}$

#### leakage

- Una vez terminada la conmutación el CMOS queda en un estado estable como el mostrado en la figura de la derecha.

- La Potencia de leakage es li-<sup>Vin</sup> nealmente dependiente de la ten o sión de alimentación, de acuerdo con una expresión bastante simple:

$$P_{stat} = I_{leakage}.V_{DD},$$

(12)

Y la Energía de leakage es el producto de la Potencia de leakage por el período de operación.

- Una vez terminada la conmutación el CMOS queda en un estado estable como el mostrado en la figura de la derecha.

- La Potencia de leakage es li-<sup>Vin</sup>

nealmente dependiente de la ten

sión de alimentación, de acuerdo con una expresión bastante

simple:

$$P_{stat} = I_{leakage}.V_{DD},$$

(12)

- Y la Energía de leakage es el producto de la Potencia de leakage por el período de operación.

- Para calcularlas a nivel del chip todas las fórmulas se multiplican por la cantidad N de nodos.

Las dimensiones del ancho del gate y del espesor la capa de óxido del transistor CMOS disminuyen linealmente con el avance en el scaling.

- Las dimensiones del ancho del gate y del espesor la capa de óxido del transistor CMOS disminuyen linealmente con el avance en el scaling.

- No así la tensión de alimentación.

- Las dimensiones del ancho del gate y del espesor la capa de óxido del transistor CMOS disminuyen linealmente con el avance en el scaling.

- No así la tensión de alimentación.

- Por ello la potencia disipada no disminuye con el scaling, ya que la cantidad de Nodo por área aumenta mas de lo que disminuyen algunos de los drivers de la Potencia Disipada.

- Las dimensiones del ancho del gate y del espesor la capa de óxido del transistor CMOS disminuyen linealmente con el avance en el scaling.

- No así la tensión de alimentación.

- Por ello la potencia disipada no disminuye con el scaling, ya que la cantidad de Nodo por área aumenta mas de lo que disminuyen algunos de los drivers de la Potencia Disipada.

- Si bien estos problemas son mas graves en los microprocesadores, han afectado también a las memorias.

$$E_{Tot} = \left[\frac{1}{2}.C_{tot}.V_{DD}^{2}.f + N_{tot}.I_{leakage}.V_{DD}\right].T \tag{13}$$

• En resumen, la energía Total consumida por un chip está dada por:

$$E_{Tot} = \left[\frac{1}{2}.C_{tot}.V_{DD}^{2}.f + N_{tot}.I_{leakage}.V_{DD}\right].T \tag{13}$$

N<sub>tot</sub> es la cantidad de nodos del chip, C<sub>tot</sub> es la suma de todas las cargas capacitivas en los N<sub>tot</sub> nodos, y T el período de operación, durante el cual, la corriente de leakage no cesa de drenar.

$$E_{Tot} = \left[\frac{1}{2}.C_{tot}.V_{DD}^{2}.f + N_{tot}.I_{leakage}.V_{DD}\right].T \tag{13}$$

- N<sub>tot</sub> es la cantidad de nodos del chip, C<sub>tot</sub> es la suma de todas las cargas capacitivas en los N<sub>tot</sub> nodos, y T el período de operación, durante el cual, la corriente de leakage no cesa de drenar.

- Cuando la carga de trabajo es baja los circuitos integrados siguen conmutando aunque no cambien el estado de sus salidas, consumiendo energía para nada.

$$E_{Tot} = \left[\frac{1}{2}.C_{tot}.V_{DD}^{2}.f + N_{tot}.I_{leakage}.V_{DD}\right].T \tag{13}$$

- N<sub>tot</sub> es la cantidad de nodos del chip, C<sub>tot</sub> es la suma de todas las cargas capacitivas en los N<sub>tot</sub> nodos, y T el período de operación, durante el cual, la corriente de leakage no cesa de drenar.

- Cuando la carga de trabajo es baja los circuitos integrados siguen conmutando aunque no cambien el estado de sus salidas, consumiendo energía para nada.

- Una solución es inhibir la frecuencia de clock (clock gating) en los momentos de baja carga para disminuir la pérdida de energía cuando el chip está inactivo.

$$E_{Tot} = \left[\frac{1}{2}.C_{tot}.V_{DD}^{2}.f + N_{tot}.I_{leakage}.V_{DD}\right].T$$

(13)

- N<sub>tot</sub> es la cantidad de nodos del chip, C<sub>tot</sub> es la suma de todas las cargas capacitivas en los N<sub>tot</sub> nodos, y T el período de operación, durante el cual, la corriente de leakage no cesa de drenar.

- Cuando la carga de trabajo es baja los circuitos integrados siguen conmutando aunque no cambien el estado de sus salidas, consumiendo energía para nada.

- Una solución es inhibir la frecuencia de clock (clock gating) en los momentos de baja carga para disminuir la pérdida de energía cuando el chip está inactivo.

- Para bajar la componente estática solo queda disminuir  $V_{DD}$ .

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- 3 Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

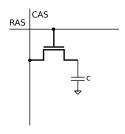

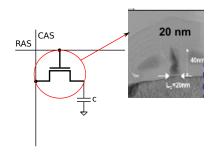

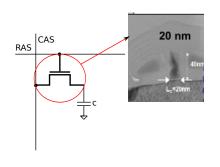

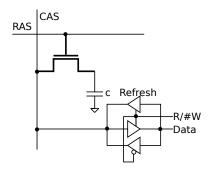

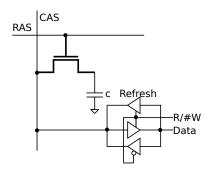

Almacena la información en forma de estado de carga en un capacitor y la sostiene durante un breve lapso con la ayuda de un transistor.

- Almacena la información en forma de estado de carga en un capacitor y la sostiene durante un breve lapso con la ayuda de un transistor.

- Una celda (un bit) se implementa con un solo transistor

máxima capacidad de almacenamiento por CI.

- Almacena la información en forma de estado de carga en un capacitor y la sostiene durante un breve lapso con la ayuda de un transistor.

- Una celda (un bit) se implementa con un solo transistor

máxima capacidad de almacenamiento por CI.

- Ese transistor está generalmente en estado de Corte. Consume mínima energía.

Almacena la información en forma de estado de carga en un capacitor y la sostiene durante un breve lapso con la ayuda de un transistor.

- Almacena la información en forma de estado de carga en un capacitor y la sostiene durante un breve lapso con la ayuda de un transistor.

- Una celda (un bit) se implementa con un solo transistor

máxima capacidad de almacenamiento por CI.

- Almacena la información en forma de estado de carga en un capacitor y la sostiene durante un breve lapso con la ayuda de un transistor.

- Una celda (un bit) se implementa con un solo transistor

máxima capacidad de almacenamiento por CI.

- Ese transistor está generalmente en estado de Corte. Consume mínima energía.

CAS

CAS

C Refresh

R/#W

Data

Al leer el bit, se descarga la capacidad (lectura destructiva).

- Al leer el bit, se descarga la capacidad (lectura destructiva).

- Necesita regenerar la carga cada vez que se la lee.

- Al leer el bit, se descarga la capacidad (lectura destructiva).

- Necesita regenerar la carga cada vez que se la lee.

- Esta operación se realiza por realimentación mediante buffers.

# Memorias dinámicas

- Al leer el bit, se descarga la capacidad (lectura destructiva).

- Necesita regenerar la carga cada vez que se la lee.

- Esta operación se realiza por realimentación mediante buffers.

- Aumenta entonces el tiempo total que demanda el acceso de la celda, ya que no libera la operación hasta no haber repuesto el estado de carga del capacitor.

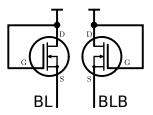

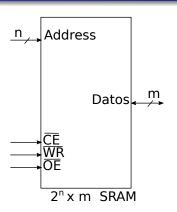

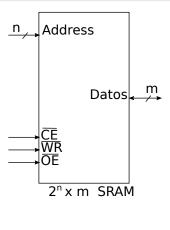

• Almacena la información en un biestable.

- Almacena la información en un biestable.

- Una celda (un bit) se compone de seis transistores. Por lo tanto tiene menor capacidad de almacenamiento por CI.

- Almacena la información en un biestable.

- Una celda (un bit) se compone de seis transistores. Por lo tanto tiene menor capacidad de almacenamiento por CI.

- Tres de los seis transistores están saturados (conducen la máxima corriente posible en forma permanente) y los otros tres al corte (conducen una corriente prácticamente insignificante, pero no nula). Esto genera mayor consumo de energía por celda.

- Almacena la información en un biestable.

- Una celda (un bit) se compone de seis transistores. Por lo tanto tiene menor capacidad de almacenamiento por CI.

- Tres de los seis transistores están saturados (conducen la máxima corriente posible en forma permanente) y los otros tres al corte (conducen una corriente prácticamente insignificante, pero no nula). Esto genera mayor consumo de energía por celda.

- La lectura es directa y no destructiva por lo cual el tiempo de acceso es muy bajo en comparación con las memorias dinámicas.

De hecho, luego de los registros del procesador, son el medio de almacenamiento de menor tiempo de acceso.

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- 3 Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

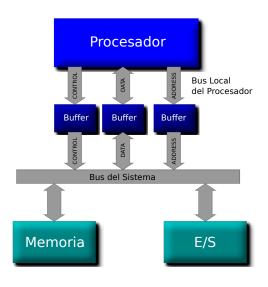

# Conexión básica (Según Von Newmann)

Desde fines de los años 80, los procesadores desarrollaban velocidades muy superiores a los tiempos de acceso a memoria.

# Conexión básica (Según Von Newmann)

- Desde fines de los años 80, los procesadores desarrollaban velocidades muy superiores a los tiempos de acceso a memoria.

- En este escenario, el procesador necesita generar wait states para esperar que la memoria esté lista ("READY") para el acceso.

# Conexión básica (Según Von Newmann)

- Desde fines de los años 80, los procesadores desarrollaban velocidades muy superiores a los tiempos de acceso a memoria.

- En este escenario, el procesador necesita generar wait states para esperar que la memoria esté lista ("READY") para el acceso.

- ¿Tiene sentido lograr altos clocks en los procesadores si no puede aprovecharlos por tener que esperar (wait) a la memoria?

El problema consiste en decidir que tipo de RAM usar en el sistema. Hay dos opciones. . .

RAM dinámica (DRAM)

RAM estática (SRAM)

- RAM dinámica (DRAM)

- Consumo mínimo.

- RAM estática (SRAM)

- Alto consumo relativo.

- RAM dinámica (DRAM)

- Consumo mínimo.

- Capacidad de almacenamiento comparativamente alta.

- RAM estática (SRAM)

- Alto consumo relativo.

- Capacidad de almacenamiento comparativamente baja.

- RAM dinámica (DRAM)

- Consumo mínimo.

- Capacidad de almacenamiento comparativamente alta.

- Costo por bit bajo.

- RAM estática (SRAM)

- Alto consumo relativo.

- Capacidad de almacenamiento comparativamente baja.

- Costo por bit alto.

- RAM dinámica (DRAM)

- Consumo mínimo.

- Capacidad de almacenamiento comparativamente alta.

- Costo por bit bajo.

- Tiempo de acceso alto (lento), debido al circuito de regeneración de carga.

- RAM estática (SRAM)

- Alto consumo relativo.

- Capacidad de almacenamiento comparativamente baja.

- Costo por bit alto.

- Tiempo de acceso bajo (es mas rápida).

El problema consiste en decidir que tipo de RAM usar en el sistema. Hay dos opciones...

- RAM dinámica (DRAM)

- Consumo mínimo.

- Capacidad de almacenamiento comparativamente alta.

- Costo por bit bajo.

- Tiempo de acceso alto (lento), debido al circuito de regeneración de carga.

- RAM estática (SRAM)

- Alto consumo relativo.

- Capacidad de almacenamiento comparativamente baja.

- Costo por bit alto.

- Tiempo de acceso bajo (es mas rápida).

#### Conclusión:

Si construimos el banco de memoria utilizando RAM estática, el costo y el consumo de la computadora son altos. Si construimos el banco de memoria utilizando RAM dinámica, no aprovechamos la velocidad del procesador.

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- 3 Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

Se trata de un banco de SRAM de muy alta velocidad, que contiene una copia de los datos e instrucciones que están en memoria principal.

- Se trata de un banco de SRAM de muy alta velocidad, que contiene una copia de los datos e instrucciones que están en memoria principal.

- El arte consiste en que esta copia esté disponible justo cuando el procesador la necesita permitiéndole acceder a esos ítems sin recurrir a wait states.

- Se trata de un banco de SRAM de muy alta velocidad, que contiene una copia de los datos e instrucciones que están en memoria principal.

- El arte consiste en que esta copia esté disponible justo cuando el procesador la necesita permitiéndole acceder a esos ítems sin recurrir a wait states.

- Combinada con una gran cantidad de memoria DRAM, para almacenar el resto de códigos y datos, resuelve el problema mediante una solución de compromiso típica.

- Se trata de un banco de SRAM de muy alta velocidad, que contiene una copia de los datos e instrucciones que están en memoria principal.

- El arte consiste en que esta copia esté disponible justo cuando el procesador la necesita permitiéndole acceder a esos ítems sin recurrir a wait states.

- Combinada con una gran cantidad de memoria DRAM, para almacenar el resto de códigos y datos, resuelve el problema mediante una solución de compromiso típica.

- Requiere de hardware adicional que asegure que este pequeño banco de memoria cache contenga los datos e instrucciones mas frecuentemente utilizados por el procesador.

# Características y métricas

#### El tamaño del banco de memoria cache debe ser:

- Suficientemente grande para que el procesador resuelva la mayor cantidad posible de búsquedas de código y datos en esta memoria asegurando una alta performance.

- Suficientemente pequeña para no afectar el consumo ni el costo del sistema.

- Hit cuando se accede a un ítem (dato o código) y éste se encuentra en la memoria cache

- Miss cuando se accede a un ítem (dato o código) y éste *no se* encuentra en la memoria cache

- hit rate hitrate = Cantidad de Accesos con hit Cantidad de Accesos Totales

Se espera un hit rate lo mas alto posible

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- 3 Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

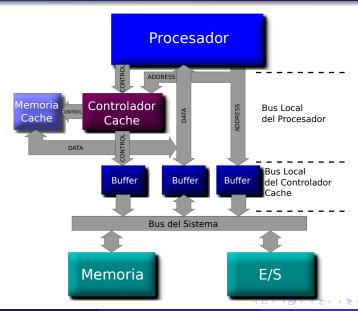

#### Subsistema Cache de Hardware

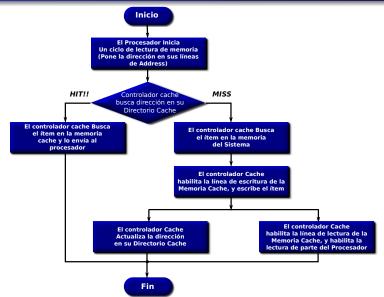

# Operación de acceso a memoria para lectura

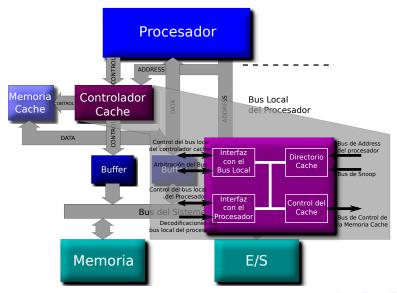

#### El Controlador Cache

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

La disminución del ancho del gate de un CMOS fuerza la disminución de la tensión de umbral que contra-intuitivamente termina aumentando la corriente de leakage.

- La disminución del ancho del gate de un CMOS fuerza la disminución de la tensión de umbral que contra-intuitivamente termina aumentando la corriente de leakage.

- El estado lógico de un bit de memoria SRAM es finalmente una acumulación de cargas en un circuito capaz de mantener su estado. Si los transistores son mas pequeños, la cantidad de carga que compone un estado lógico es menor lo que la hace mas factible de ser alteradas por fenómenos externos (EMI Por ejemplo).

- La disminución del ancho del gate de un CMOS fuerza la disminución de la tensión de umbral que contra-intuitivamente termina aumentando la corriente de leakage.

- El estado lógico de un bit de memoria SRAM es finalmente una acumulación de cargas en un circuito capaz de mantener su estado. Si los transistores son mas pequeños, la cantidad de carga que compone un estado lógico es menor lo que la hace mas factible de ser alteradas por fenómenos externos (EMI Por ejemplo).

- El proceso de fabricación debe necesariamente variar cuando se reduce el transistor. Esto genera diferencias entre el modelo diseñado y el obtenido

- La disminución del ancho del gate de un CMOS fuerza la disminución de la tensión de umbral que contra-intuitivamente termina aumentando la corriente de leakage.

- El estado lógico de un bit de memoria SRAM es finalmente una acumulación de cargas en un circuito capaz de mantener su estado. Si los transistores son mas pequeños, la cantidad de carga que compone un estado lógico es menor lo que la hace mas factible de ser alteradas por fenómenos externos (EMI Por ejemplo).

- El proceso de fabricación debe necesariamente variar cuando se reduce el transistor. Esto genera diferencias entre el modelo diseñado y el obtenido

- Los caminos de conexión de transistores (wires), comienzan a ser significativos en términos de delay y de disipación.

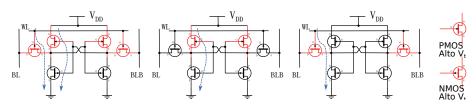

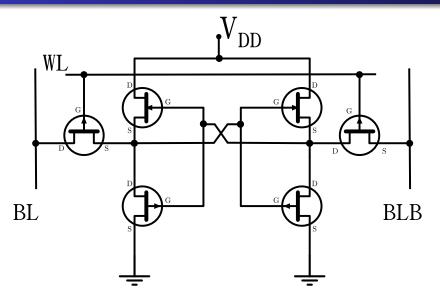

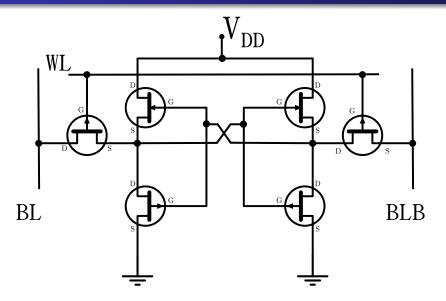

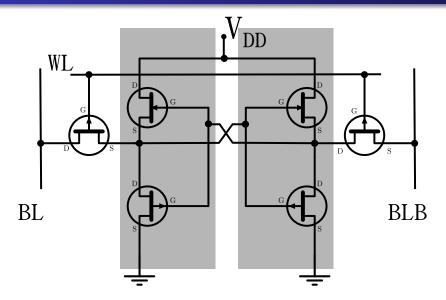

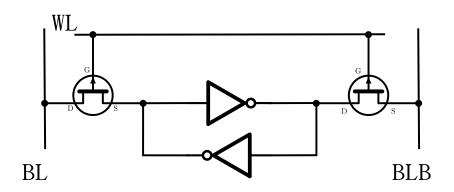

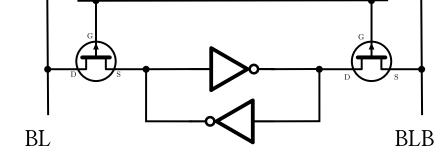

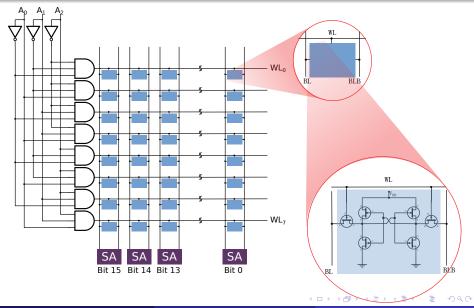

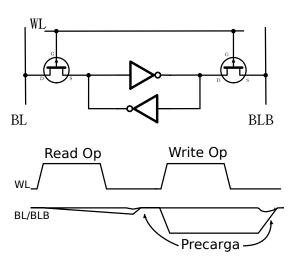

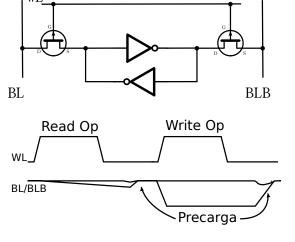

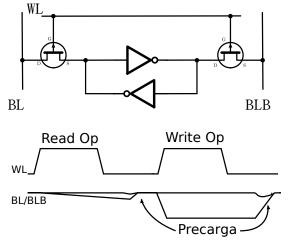

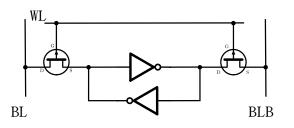

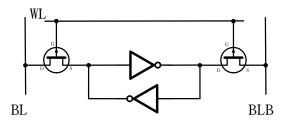

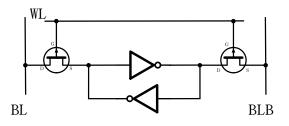

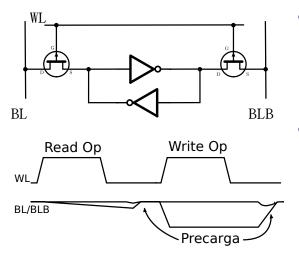

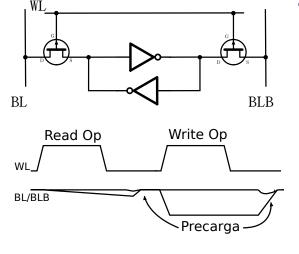

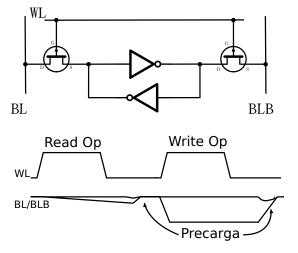

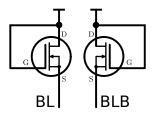

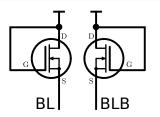

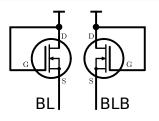

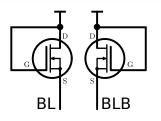

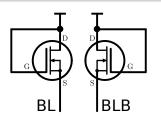

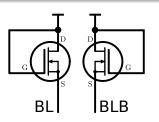

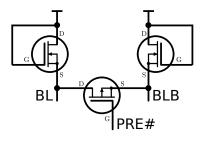

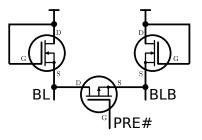

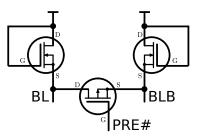

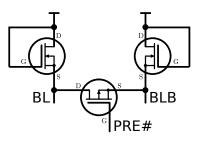

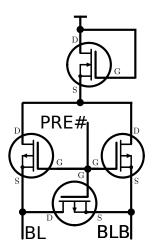

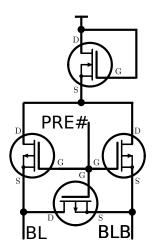

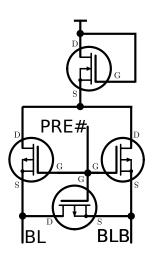

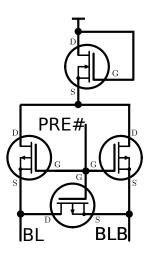

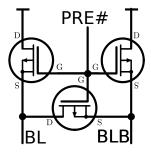

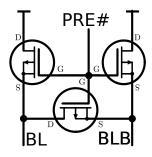

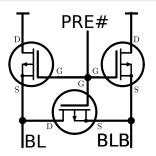

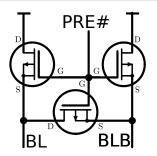

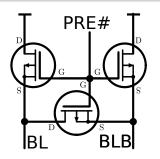

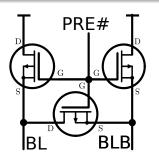

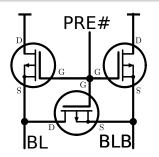

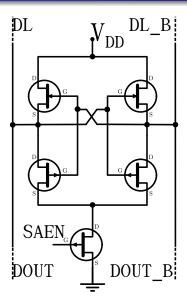

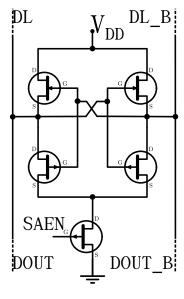

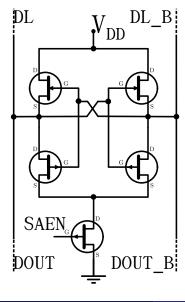

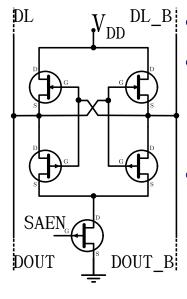

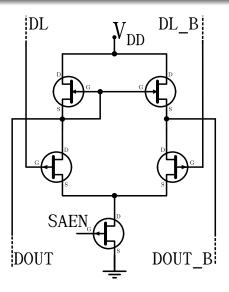

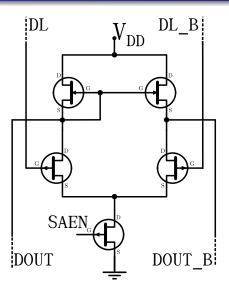

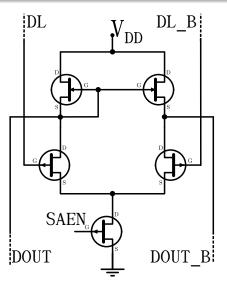

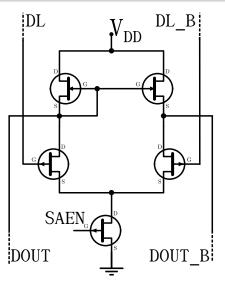

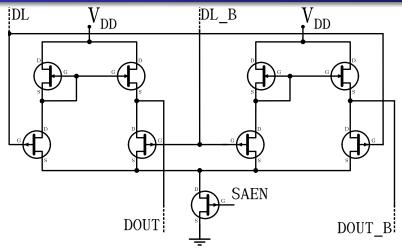

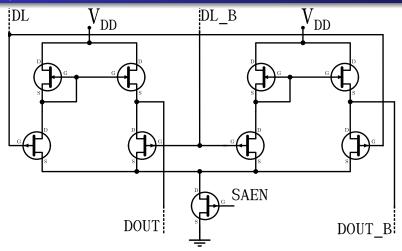

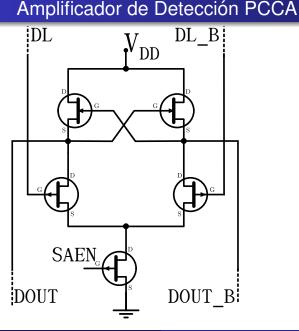

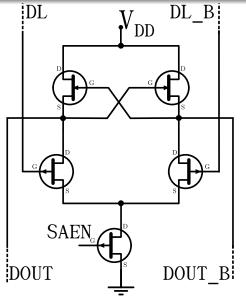

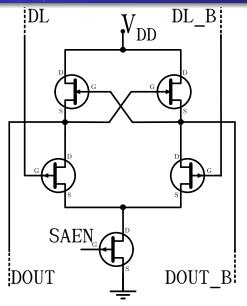

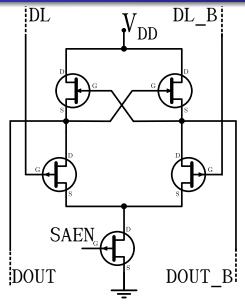

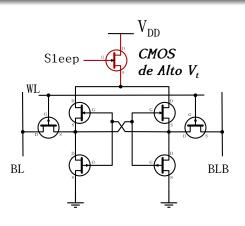

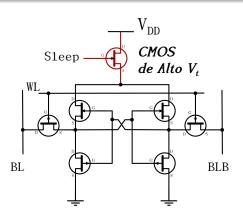

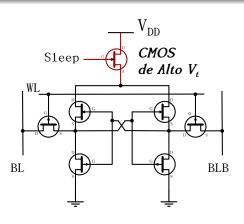

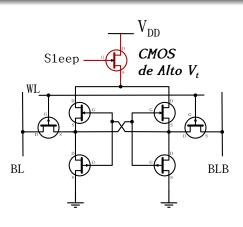

### Celda de un bit de SRAM

#### Celda de un bit de SRAM

#### Celda de un bit de SRAM

#### Celda de un bit de SRAM

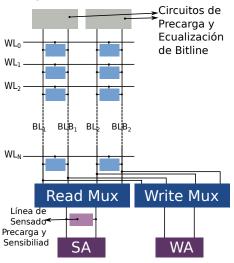

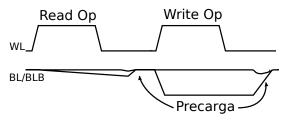

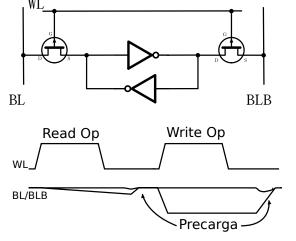

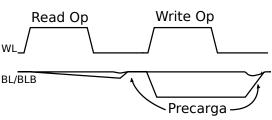

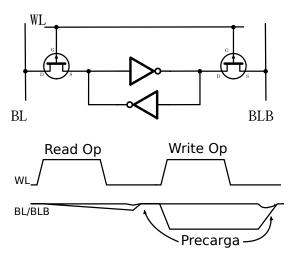

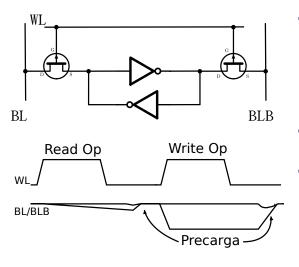

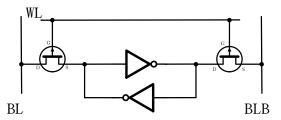

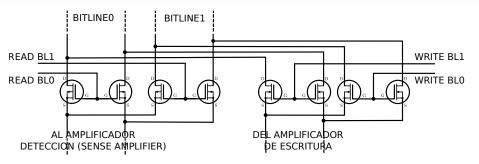

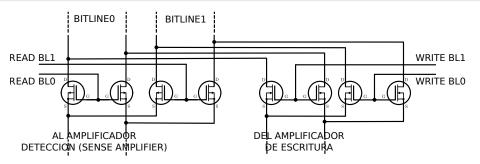

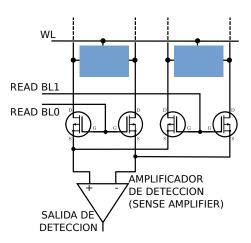

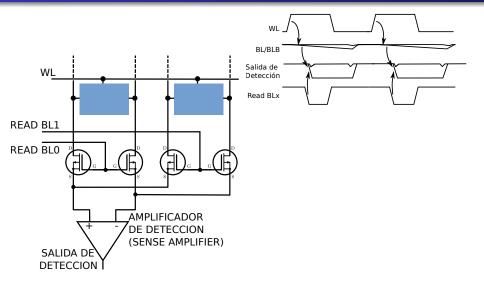

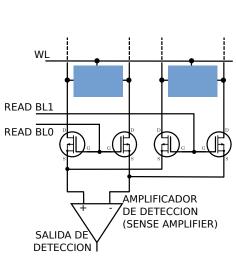

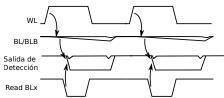

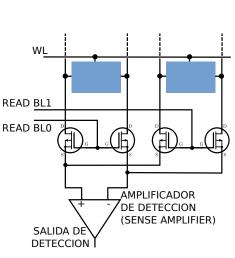

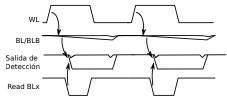

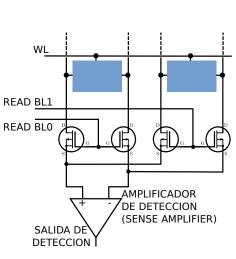

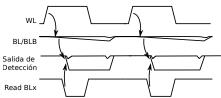

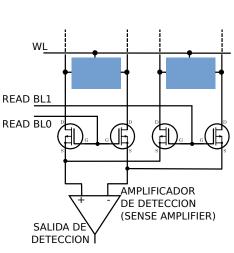

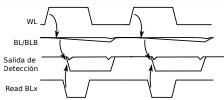

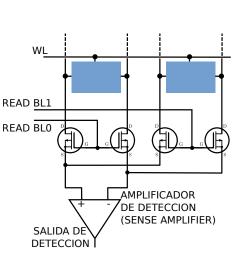

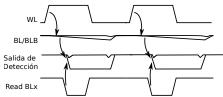

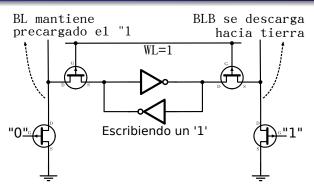

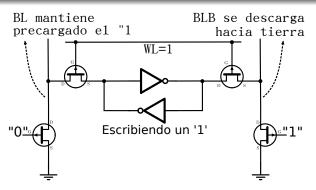

La lectura del bit se realiza activando **WL**, y detectando la tensión diferencial entre el par de Líneas de Bit (**BL**y **BLB**), inicialmente precargadas para entregar un '1'.

#### Celda de un bit de SRAM

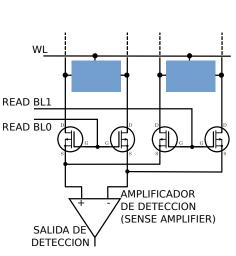

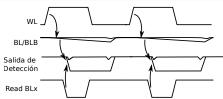

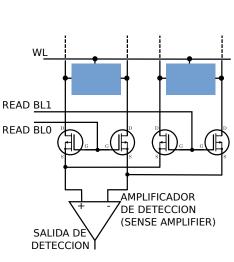

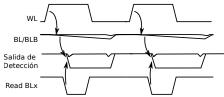

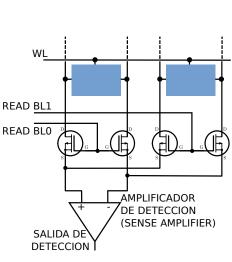

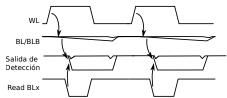

La escritura del bit se realiza activando **WL**, y colocando una tensión diferencial entre el par de Líneas de Bit (**BL**y **BLB**) proveniente de una fuente externa que fuerce el nuevo estado en el biestable.

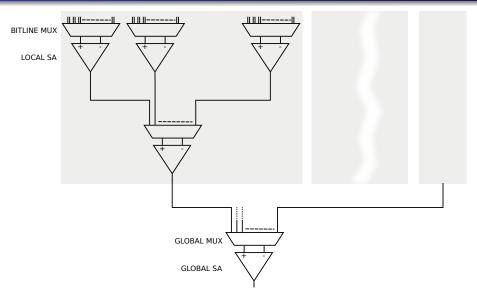

#### **Temario**

- Introducción

- Rol de la memoria en un computador

- Clasificación

- 2 Jerarquía de memoria

- Fundamentación

- Métricas

- Arquitecturas jerárquicas

- 3 Consumo

- Potencia y Energía (once again...)

- Memorias volátiles

- Clasificación tecnológica

- Memorias y velocidad del Procesador

- Memoria Cache

- Principio de Funcionamiento

- Hardware dedicado = + complejidad

- 6 SRAM Cuestiones de Implementación

- Vistazo introductorio

- Decodificación

- Circuitos periféricos

- Timing Conexión física

- Tópicos avanzados de implementación

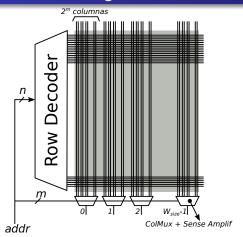

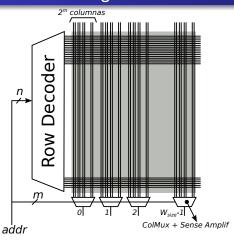

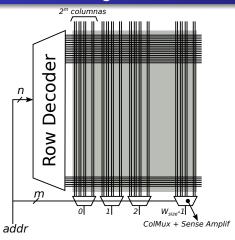

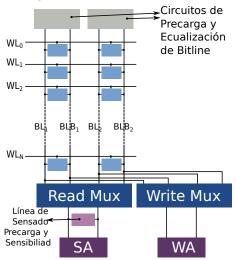

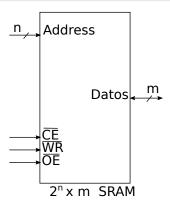

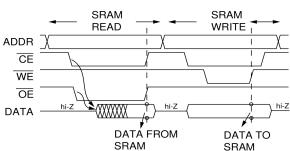

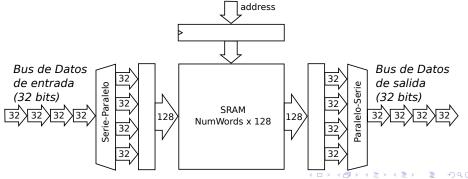

La decodificación de direcciones es un proceso sencillo que consiste en tomar el valor lógico de una dirección de memoria y a partir de éste valor y las señales de control del bus activar las señales lógicas necesarias para realizar la operación solicitada en la posición de memoria indicada.

- La decodificación de direcciones es un proceso sencillo que consiste en tomar el valor lógico de una dirección de memoria y a partir de éste valor y las señales de control del bus activar las señales lógicas necesarias para realizar la operación solicitada en la posición de memoria indicada.

- La forma mas simple de implementarla es inyectando la dirección de n bits en un decodificador de n a 2<sup>n</sup>.

- La decodificación de direcciones es un proceso sencillo que consiste en tomar el valor lógico de una dirección de memoria y a partir de éste valor y las señales de control del bus activar las señales lógicas necesarias para realizar la operación solicitada en la posición de memoria indicada.

- La forma mas simple de implementarla es inyectando la dirección de n bits en un decodificador de n a 2<sup>n</sup>.

- Esto involucra una operación AND sobre los valores posibles de entrada cuya salida active solo la WL correspondiente a la celda direccionada.

- La decodificación de direcciones es un proceso sencillo que consiste en tomar el valor lógico de una dirección de memoria y a partir de éste valor y las señales de control del bus activar las señales lógicas necesarias para realizar la operación solicitada en la posición de memoria indicada.

- La forma mas simple de implementarla es inyectando la dirección de n bits en un decodificador de n a 2<sup>n</sup>.

- Esto involucra una operación AND sobre los valores posibles de entrada cuya salida active solo la WL correspondiente a la celda direccionada.

- A continuación un caso sencillo para un bus de address de 3 líneas,  $A_2,\,A_1,\,A_0$

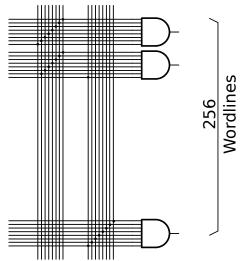

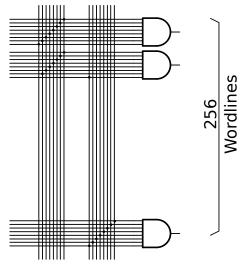

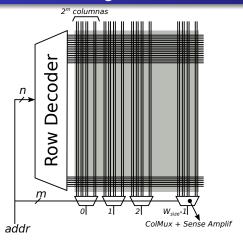

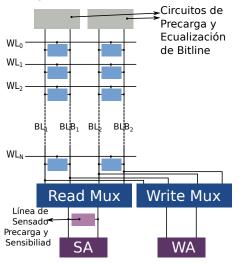

La principal preocupación de diseño son los requerimientos de Fan-in y Fan-out en situaciones reales en donde la matriz representada en el gráfico anterior escala geométricamente confirme aumentan las lineas de Address.

- La principal preocupación de diseño son los requerimientos de Fan-in y Fan-out en situaciones reales en donde la matriz representada en el gráfico anterior escala geométricamente confirme aumentan las lineas de Address.

- Esto impide por ineficiente un diseño con un solo nivel de compuertas AND.

- La principal preocupación de diseño son los requerimientos de Fan-in y Fan-out en situaciones reales en donde la matriz representada en el gráfico anterior escala geométricamente confirme aumentan las lineas de Address.

- Esto impide por ineficiente un diseño con un solo nivel de compuertas AND.

- Los decodificadores reales Se implementan con estructuras multinivel de compuertas AND.

- La principal preocupación de diseño son los requerimientos de Fan-in y Fan-out en situaciones reales en donde la matriz representada en el gráfico anterior escala geométricamente confirme aumentan las lineas de Address.

- Esto impide por ineficiente un diseño con un solo nivel de compuertas AND.

- Los decodificadores reales Se implementan con estructuras multinivel de compuertas AND.

- Es tan no trivial este tema que el diseño del decodificador interno es crítico tanto en el delay de escritura y lectura (tiempo de acceso) como en disipación de energía.

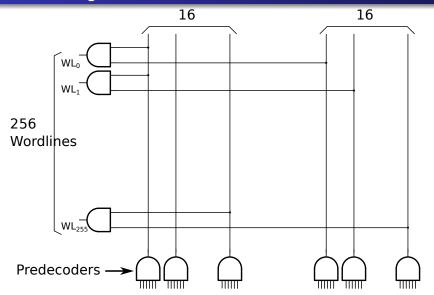

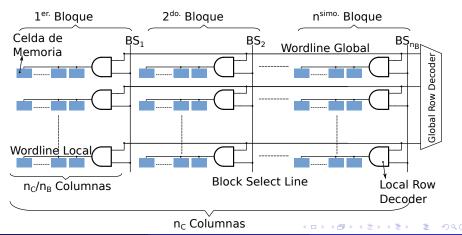

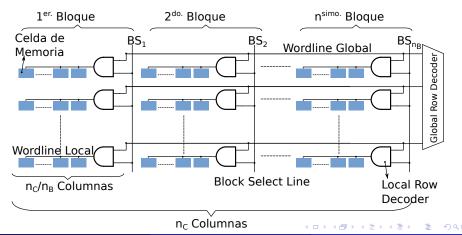

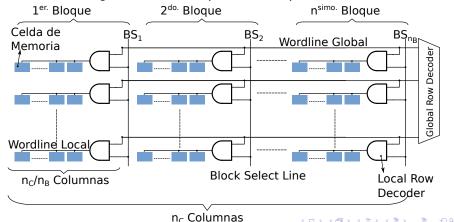

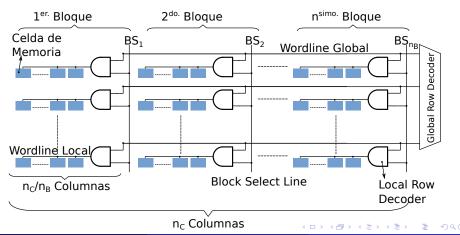

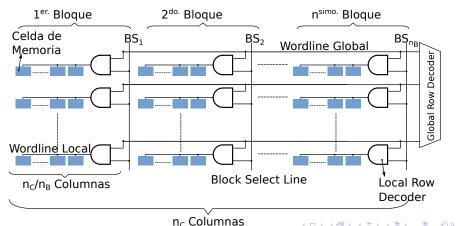

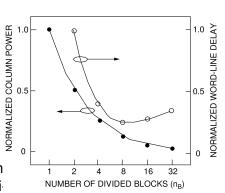

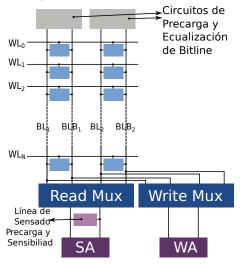

• Es la salida al problema descripto.

- Es la salida al problema descripto.

- Se basa en evitar recurrir a compuertas de alto Fan-in, debido a las enormes dificultades de diseño y a su baja eficiencia.

- Es la salida al problema descripto.

- Se basa en evitar recurrir a compuertas de alto Fan-in, debido a las enormes dificultades de diseño y a su baja eficiencia.

- Predecoding hace una decodificación en dos etapas.

- Es la salida al problema descripto.

- Se basa en evitar recurrir a compuertas de alto Fan-in, debido a las enormes dificultades de diseño y a su baja eficiencia.

- Predecoding hace una decodificación en dos etapas.

- La primera involucra la función AND sobre un grupo de entradas (no todas sino por ejemplo las mas significativas).

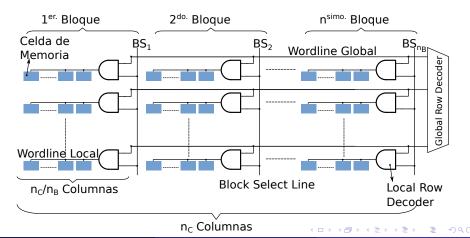

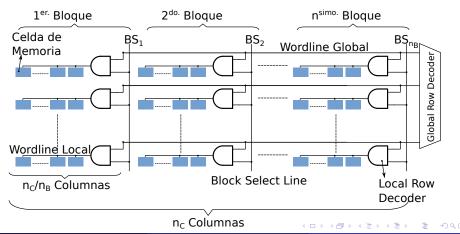

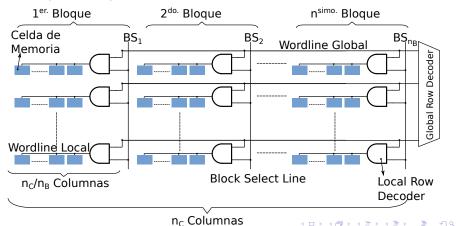

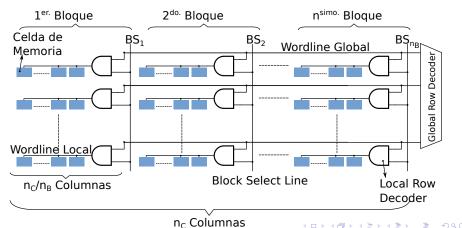

- Es la salida al problema descripto.