## Buses de Sistemas

# Buses de Interconexión para SoC

Alejandro Furfaro

6 de octubre de 2020

### **Temario**

- Vistazo General

- Bus AMBA

- Protocolos AMBA

- AMBA V2+

- Bus de Sistema de Alta performance

- Bus de Periféricos simples

- Lineamientos para organizar un Bus

- Señalización

- Funcionamiento y Operación

- AXI

- Características

#### **Temario**

- 🚺 Vistazo General

- Bus AMBA

- Protocolos AMBA

- AMBA V2+

- Bus de Sistema de Alta performance

- Bus de Periféricos simples

- Lineamientos para organizar un Bus

- Señalización

- Funcionamiento y Operación

- 3 AX

- Características

## Principios de Diseño de un Bus

Cuando se emprende el diseño de un SOC, no solo es importante definir que bloques se van a incluir en el sistema, sino como se los va a interconectar.

## Principios de Diseño de un Bus

No es tan trivial como conectar los terminales de address data y control de cada componente y diseñar un decodificador de direcciones. Hace tiempo que es mas sofisticado que eso.

# Principios de Diseño de un Bus

Forman parte de la Arquitectura e involucran interfaces de hardware diseminadas en los diferentes componentes, lo cual les confiere independencia de los dispositivos, y controladores permitiendo interconectar de manera transparente una variedad muy heterogénea de microcontrollers, CPUs de propósito general y hasta GPU's en un mismo SOC con diversidad de dispositivos periféricos, y memorias, de diferentes velocidades de acceso y tecnologías.

• AMBA por Advanced Microcontroller Bus Architecture.

- AMBA por Advanced Microcontroller Bus Architecture.

- Estándar abierto presentado en 1996 por ARM.

- AMBA por Advanced Microcontroller Bus Architecture.

- Estándar abierto presentado en 1996 por ARM.

- Objeto: Conectar y controlar los periféricos y bloques que se conectan a una CPU en el interior de un SoC.

- AMBA por Advanced Microcontroller Bus Architecture.

- Estándar abierto presentado en 1996 por ARM.

- Objeto: Conectar y controlar los periféricos y bloques que se conectan a una CPU en el interior de un SoC.

- Escaló desde microcontroladores hasta procesadores de alta performance, incluso con soporte para SMP y AMP.

- AMBA por Advanced Microcontroller Bus Architecture.

- Estándar abierto presentado en 1996 por ARM.

- Objeto: Conectar y controlar los periféricos y bloques que se conectan a una CPU en el interior de un SoC.

- Escaló desde microcontroladores hasta procesadores de alta performance, incluso con soporte para SMP y AMP.

- La primer versión de la especificación cubrió dos versiones:

- AMBA por Advanced Microcontroller Bus Architecture.

- Estándar abierto presentado en 1996 por ARM.

- Objeto: Conectar y controlar los periféricos y bloques que se conectan a una CPU en el interior de un SoC.

- Escaló desde microcontroladores hasta procesadores de alta performance, incluso con soporte para SMP y AMP.

- La primer versión de la especificación cubrió dos versiones:

- √ "Advanced System Bus" (ASB),

- AMBA por Advanced Microcontroller Bus Architecture.

- Estándar abierto presentado en 1996 por ARM.

- Objeto: Conectar y controlar los periféricos y bloques que se conectan a una CPU en el interior de un SoC.

- Escaló desde microcontroladores hasta procesadores de alta performance, incluso con soporte para SMP y AMP.

- La primer versión de la especificación cubrió dos versiones:

- √ "Advanced System Bus" (ASB),

- √ "Advanced Periferal Bus" (APB).

- AMBA por Advanced Microcontroller Bus Architecture.

- Estándar abierto presentado en 1996 por ARM.

- Objeto: Conectar y controlar los periféricos y bloques que se conectan a una CPU en el interior de un SoC.

- Escaló desde microcontroladores hasta procesadores de alta performance, incluso con soporte para SMP y AMP.

- La primer versión de la especificación cubrió dos versiones:

- √ "Advanced System Bus" (ASB),

- √ "Advanced Periferal Bus" (APB).

- La segunda versión, de 1999, es hoy un estándar de facto en Microcontrollers: AHB (Advanced High-Performance Bus), que trabaja en único flanco de clock.

- AMBA por Advanced Microcontroller Bus Architecture.

- Estándar abierto presentado en 1996 por ARM.

- Objeto: Conectar y controlar los periféricos y bloques que se conectan a una CPU en el interior de un SoC.

- Escaló desde microcontroladores hasta procesadores de alta performance, incluse con seporte para SMP y AMP.

- La primer versión de la especificación cubrió dos versiones:

- √ "Advanced System Bus" (ASB),

- √ "Advanced Periferal Bus" (APB).

- La segunda versión, de 1999, es hoy un estándar de facto en Microcontrollers: AHB (Advanced High-Performance Bus), que trabaja en único flanco de clock.

- No solo ARM utiliza estos buses. Leon II y III utilizan AHB, y APB.

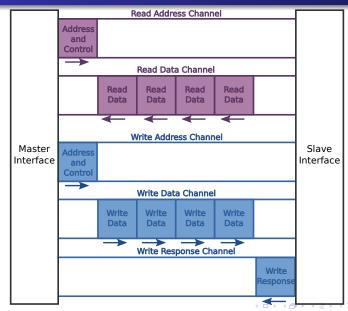

La versión 3 de AMBA introduce AXI: Advanced eXtensible Interface, con el propósito de lograr mayor performance en la interconexión, y ATB: Advanced Trace Bus como parte de la interfaz CoreSight on chip para debug y Trace.

- La versión 3 de AMBA introduce AXI: Advanced eXtensible Interface, con el propósito de lograr mayor performance en la interconexión, y ATB: Advanced Trace Bus como parte de la interfaz CoreSight on chip para debug y Trace.

- En 2010 se libera AMBA v4, inicialmente con AXI4, completada en 2011 con AXI ACE (por AXI Advanced Coherency Extensions) que proporciona coherencia para todo el resto del sistema AMBA 4.

- La versión 3 de AMBA introduce AXI: Advanced eXtensible Interface, con el propósito de lograr mayor performance en la interconexión, y ATB: Advanced Trace Bus como parte de la interfaz CoreSight on chip para debug y Trace.

- En 2010 se libera AMBA v4, inicialmente con AXI4, completada en 2011 con **AXI ACE** (por **AXI A**dvanced **C**oherency **E**xtensions) que proporciona coherencia para todo el resto del sistema AMBA 4.

- En 2013 se presenta AMBA 5 Coherent Hub Interface (CHI) con un fuerte rediseño de alta velocidad en la capa de transporte y eliminación de congestiones.

### **Temario**

- Vistazo Genera

- Bus AMBA

- Protocolos AMBA

- AMBA V2+

- Bus de Sistema de Alta performance

- Bus de Periféricos simples

- Lineamientos para organizar un Bus

- Señalización

- Funcionamiento y Operación

- 3 AX

- Características

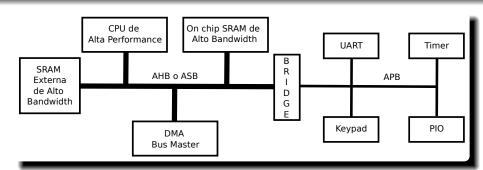

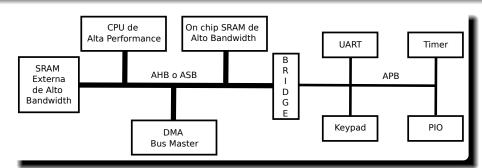

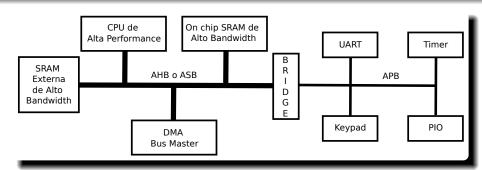

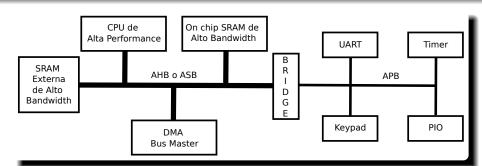

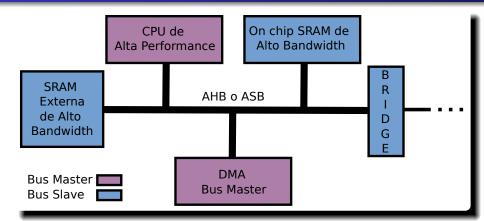

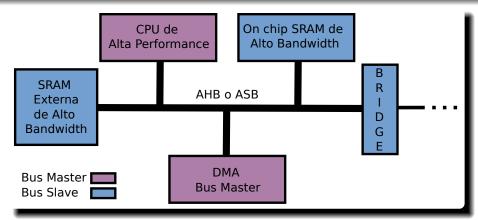

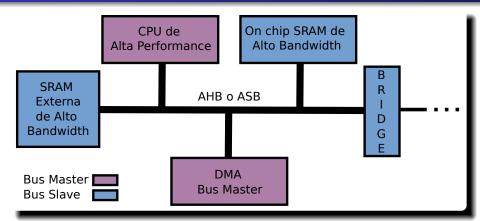

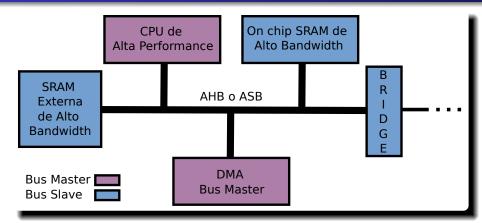

La especificación AMBA v2, contiene tres protocolos

La especificación AMBA v2, contiene tres protocolos

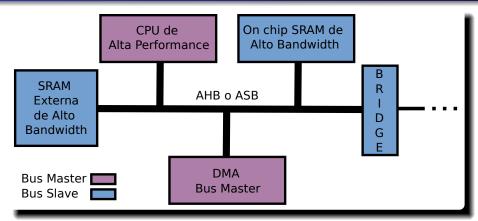

Advanced High-Performance Bus (AHB): Protocolo para interconexión de módulos de alta frecuencia y alta performance introducido en AMBAv2. Interconecta CPU's, módulos de memoria on-chip y off-chip, con interfaces de periféricos de macrocelda de baja potencia. Introduce nuevas técnicas de síntesis y testing que permiten agilizar y simplificar los diseños.

La especificación AMBA v2, contiene tres protocolos

- Advanced High-Performance Bus (AHB): Protocolo para interconexión de módulos de alta frecuencia y alta performance introducido en AMBAv2. Interconecta CPU's, módulos de memoria on-chip y off-chip, con interfaces de periféricos de macrocelda de baja potencia. Introduce nuevas técnicas de síntesis y testing que permiten agilizar y simplificar los diseños.

- Advanced System Bus (ASB): Protocolo original para módulos de alta performance. Interconecta CPU's, módulos de memoria on-chip y off-chip, con interfaces de periféricos de macrocelda de baja potencia. Puede aplicarse cuando no son necesarias las nuevas funciones de AHB.

La especificación AMBA v2, contiene tres protocolos

- Advanced High-Performance Bus (AHB): Protocolo para interconexión de módulos de alta frecuencia y alta performance introducido en AMBAv2. Interconecta CPU's, módulos de memoria on-chip y off-chip, con interfaces de periféricos de macrocelda de baja potencia. Introduce nuevas técnicas de síntesis y testing que permiten agilizar y simplificar los diseños.

- Advanced System Bus (ASB): Protocolo original para módulos de alta performance. Interconecta CPU's, módulos de memoria on-chip y off-chip, con interfaces de periféricos de macrocelda de baja potencia. Puede aplicarse cuando no son necesarias las nuevas funciones de AHB.

- Advanced Peripheral Bus (APB): Protocolo pensado para conectar dispositivos periféricos de baja potencia y complejidad.

Puede utilizarse en conjunto con cualquier otra versión del Bus del Sistema.

Alto rendimiento

- **AHB**

- Operación en Pipeline

- Acepta Múltiples bus masters

- Transferencias Burst

- Transacciones divisibles

Alto rendimiento

- ASB

- Operación en Pipeline

- Acepta Múltiples bus masters

- Transferencias Burst

- Transacciones divisibles

- Alto rendimiento

- Operación en Pipeline

- Acepta Múltiples bus masters

- Transferencias Burst

- Transacciones divisibles

- Low power

- Address y Control Latcheados

- Interfaz Simple

- Adecuado para gran variedad de periféricos

**APB**

Bus cycle: Es la duración de un período de clock. En AHB APB y es el tiempo entre dos flancos ascendentes consecutivos. En ASB entre dos flancos ascendentes consecutivos.

- Bus cycle: Es la duración de un período de clock. En AHB APB y es el tiempo entre dos flancos ascendentes consecutivos. En ASB entre dos flancos ascendentes consecutivos.

- Bus Transfer: Es la lectura o escritura de un objeto de datos. Toma varios *Bus cycles*. Termina cuando el dispositivo Slave, responde en forma completa la transacción. Soporta 8, 16, 32, 64, y 128 bits. (ASB solo soporta 8 16 y 32 bits). En APB son lecturas y escrituras de datos e insumen dos ciclos de Bus.

- Bus cycle: Es la duración de un período de clock. En AHB APB y es el tiempo entre dos flancos ascendentes consecutivos. En ASB entre dos flancos ascendentes consecutivos.

- Bus Transfer: Es la lectura o escritura de un objeto de datos. Toma varios **Bus cycles**. Termina cuando el dispositivo Slave, responde en forma completa la transacción. Soporta 8, 16, 32, 64, y 128 bits. (ASB solo soporta 8 16 y 32 bits). En APB son lecturas y escrituras de datos e insumen dos ciclos de Bus.

- Bus operation: Soportada solo por AHB. Un Master inicia transacciones de uno a mas datos hacia o desde una zona contigua de memoria, con autoincremento de puntero en pasos determinados por el tamaño de datos (byte, halfword o word)

### **Temario**

- Vistazo General

- Bus AMBA

- Protocolos AMBA

- AMBA V2+

- Bus de Sistema de Alta performance

- Bus de Periféricos simples

- Lineamientos para organizar un Bus

- Señalización

- Funcionamiento y Operación

- 3 AX

- Características

### Bus AHB

#### Bus AHB

AHB Master es cualquier dispositivo capaz de iniciar una transacción de lectura o de escritura, proporcionando la información de dirección y de control necesaria, en las líneas de bus. Soporta conexión multi master, pero solo uno puede estar activo a la vez.

#### Bus AHB

AHB Slave es un dispositivo que responde a una transacción de lectura o escritura para el rango de direcciones dado, al que pertenece la dirección puesta en el bus por un Master al cual señaliza indicando la realización, falla, o espera de la transacción.

#### Bus AHB

AHB Arbiter es un dispositivo que arbitra el acceso al bus por parte de los diferentes AHB Master. Si bien el protocolo es fijo pueden emplearse diferentes algoritmos en base a los requerimientos particulares de cada sistema: fair access, highest priority. Debe existir aun cuando se tenga un solo Master.

#### Bus AHB

**AHB Decoder** es el encargado de decodificar la dirección de cada transferencia y generar la señal de Chip Select para el **AHB Slave** involucrado. Debe haber un único **AHB Decoder** centralizado en cualquier implementación AHB.

#### **Temario**

- Vistazo General

- Bus AMBA

- Protocolos AMBA

- AMBA V2+

- Bus de Sistema de Alta performance

- Bus de Periféricos simples

- Lineamientos para organizar un Bus

- Señalización

- Funcionamiento y Operación

- 3 AX

- Características

• Está encapsulado como un Slave del AHB.

- Está encapsulado como un Slave del AHB.

- El Bridge APB maneja el handshake con AHB/ASB, adaptando el timing y convirtiendo señales en caso de ser necesario hacia el lado APB.

- Está encapsulado como un Slave del AHB.

- El Bridge APB maneja el handshake con AHB/ASB, adaptando el timing y convirtiendo señales en caso de ser necesario hacia el lado APB.

- Al APB se conectan aquellos periféricos con bajos requerimientos de ancho de banda, performance, e interfaz de bus pipeline.

- Está encapsulado como un Slave del AHB.

- El Bridge APB maneja el handshake con AHB/ASB, adaptando el timing y convirtiendo señales en caso de ser necesario hacia el lado APB.

- Al APB se conectan aquellos periféricos con bajos requerimientos de ancho de banda, performance, e interfaz de bus pipeline.

- Todas sus transiciones se llevan a cabo en el flanco ascendente de la señal de clock.

El bridge convierte transacciones AHB/ASB en APB, latcheando todas las señales de dirección, datos, y control, y proveer un nivel de decodificación de estas mismas señales en términos del APB.

- El bridge convierte transacciones AHB/ASB en APB, latcheando todas las señales de dirección, datos, y control, y proveer un nivel de decodificación de estas mismas señales en términos del APB.

- Los dispositivos conectados al APB son Slaves del Bridge. El acceso es asincrónico controlado por handshake desde el Bridge, siendo validas durante todo el acceso las señales de Direcciones y control, y los datos solo en accesos de escritura.

- El bridge convierte transacciones AHB/ASB en APB, latcheando todas las señales de dirección, datos, y control, y proveer un nivel de decodificación de estas mismas señales en términos del APB.

- Los dispositivos conectados al APB son Slaves del Bridge. El acceso es asincrónico controlado por handshake desde el Bridge, siendo validas durante todo el acceso las señales de Direcciones y control, y los datos solo en accesos de escritura.

- El bus APB está estático (zero-powered) si no hay actividad

#### **Temario**

- Vistazo General

- Bus AMBA

- Protocolos AMBA

- AMBA V2+

- Bus de Sistema de Alta performance

- Bus de Periféricos simples

- Lineamientos para organizar un Bus

- Señalización

- Funcionamiento y Operación

- 3 AX

- Características

El diseño mas simple de un SoC es poner todos los periféricos del lado AHB. Pero:

- El diseño mas simple de un SoC es poner todos los periféricos del lado AHB. Pero:

- Se incrementa la cantidad de cargas en el Bus incrementando la disipación de potencia.

- El diseño mas simple de un SoC es poner todos los periféricos del lado AHB. Pero:

- Se incrementa la cantidad de cargas en el Bus incrementando la disipación de potencia.

- Los dispositivos mas lentos van a limitar la performance de todo el bus.

- El diseño mas simple de un SoC es poner todos los periféricos del lado AHB. Pero:

- Se incrementa la cantidad de cargas en el Bus incrementando la disipación de potencia.

- Los dispositivos mas lentos van a limitar la performance de todo el bus.

- Los dispositivos mas lentos requieren latchear señales de address y control, y el AHB está preparado en oposición para realizar transacciones pipeline.

- El diseño mas simple de un SoC es poner todos los periféricos del lado AHB. Pero:

- Se incrementa la cantidad de cargas en el Bus incrementando la disipación de potencia.

- Los dispositivos mas lentos van a limitar la performance de todo el bus.

- Los dispositivos mas lentos requieren latchear señales de address y control, y el AHB está preparado en oposición para realizar transacciones pipeline.

- El bus AHB es sincrónico mientras que muchos de los periféricos lentos son asincrónicos.

- El diseño mas simple de un SoC es poner todos los periféricos del lado AHB. Pero:

- Se incrementa la cantidad de cargas en el Bus incrementando la disipación de potencia.

- Los dispositivos mas lentos van a limitar la performance de todo el bus.

- Los dispositivos mas lentos requieren latchear señales de address y control, y el AHB está preparado en oposición para realizar transacciones pipeline.

- El bus AHB es sincrónico mientras que muchos de los periféricos lentos son asincrónicos.

- Generalmente los periféricos sencillos se activan con una señal de strobe y luego con la de lectura / escritura, sin requerimientos de clock, ni alta frecuencia.

Que se recomienda conectar en el AHB:

- Que se recomienda conectar en el AHB:

- √ Bus Masters

- Que se recomienda conectar en el AHB:

- Bus Masters

- √ Memorias on-chip

- Que se recomienda conectar en el AHB:

- Bus Masters

- ✓ Memorias on-chip

- Interfaces con Memoria externa.

- Que se recomienda conectar en el AHB:

- Bus Masters

- ✓ Memorias on-chip

- Interfaces con Memoria externa.

- Periféricos que requieren gran ancho de banda y poseen interfaces FIFO interfaces

- Que se recomienda conectar en el AHB:

- Bus Masters

- √ Memorias on-chip

- Interfaces con Memoria externa.

- Periféricos que requieren gran ancho de banda y poseen interfaces FIFO interfaces

- ✓ Periféricos Slave con DMA.

- Que se recomienda conectar en el AHB:

- Que se recomienda conectar en el APB:

- √ Bus Masters

- √ Memorias on-chip

- Interfaces con Memoria externa.

- Periféricos que requieren gran ancho de banda y poseen interfaces FIFO interfaces

- ✓ Periféricos Slave con DMA.

- Que se recomienda conectar en el AHB:

- Bus Masters

- ✓ Memorias on-chip

- Interfaces con Memoria externa.

- Periféricos que requieren gran ancho de banda y poseen interfaces FIFO interfaces

- ✓ Periféricos Slave con DMA.

- Que se recomienda conectar en el *APB*:

- Dispositivos Slave simples register mapped

- Que se recomienda conectar en el AHB:

- Bus Masters

- √ Memorias on-chip

- Interfaces con Memoria externa.

- Periféricos que requieren gran ancho de banda y poseen interfaces FIFO interfaces

- ✓ Periféricos Slave con DMA.

- Que se recomienda conectar en el APB:

- Dispositivos Slave simples register mapped

- Interfaces de muy baja potencia que requieren que no se rutee en forma global el clock.

- Que se recomienda conectar en el AHB:

- Bus Masters

- √ Memorias on-chip

- Interfaces con Memoria externa.

- Periféricos que requieren gran ancho de banda y poseen interfaces FIFO interfaces

- ✓ Periféricos Slave con DMA.

- Que se recomienda conectar en el APB:

- Dispositivos Slave simples register mapped

- Interfaces de muy baja potencia que requieren que no se rutee en forma global el clock.

- Agrupamientos de periféricos narrow-bus que eviten cargar al bus del sistema.

#### **Temario**

- Vistazo General

- Bus AMBA

- Protocolos AMBA

- AMBA V2+

- Bus de Sistema de Alta performance

- Bus de Periféricos simples

- Lineamientos para organizar un Bus

- Señalización

- Funcionamiento y Operación

- 3 AXI

- Características

Los diferentes buses manejan un grupo de señales del mismo tipo y que por lo tanto poseen el mismo nombre genérico

- Los diferentes buses manejan un grupo de señales del mismo tipo y que por lo tanto poseen el mismo nombre genérico

- La diferenciación se hace mediante un simple sistema de prefijos

- Los diferentes buses manejan un grupo de señales del mismo tipo y que por lo tanto poseen el mismo nombre genérico

- La diferenciación se hace mediante un simple sistema de prefijos

- H Para las señales del AHB

- Los diferentes buses manejan un grupo de señales del mismo tipo y que por lo tanto poseen el mismo nombre genérico

- La diferenciación se hace mediante un simple sistema de prefijos

- H Para las señales del AHB

- S Para las señales del *ASB*

- Los diferentes buses manejan un grupo de señales del mismo tipo y que por lo tanto poseen el mismo nombre genérico

- La diferenciación se hace mediante un simple sistema de prefijos

- H Para las señales del AHB

- S Para las señales del *ASB*

- P Para las señales del APB

- Los diferentes buses manejan un grupo de señales del mismo tipo y que por lo tanto poseen el mismo nombre genérico

- La diferenciación se hace mediante un simple sistema de prefijos

- H Para las señales del *AHB*

- S Para las señales del *ASB*

- P Para las señales del *APB*

- A Para las señales del AXI

- Los diferentes buses manejan un grupo de señales del mismo tipo y que por lo tanto poseen el mismo nombre genérico

- La diferenciación se hace mediante un simple sistema de prefijos

- H Para las señales del *AHB*

- S Para las señales del *ASB*

- P Para las señales del APB

- A Para las señales del **AXI**

- Por ejemplo HADDR[31:0] y PADDR[31:0] son las líneas de Address del AHB y APB respectivamente.

- Los diferentes buses manejan un grupo de señales del mismo tipo y que por lo tanto poseen el mismo nombre genérico

- La diferenciación se hace mediante un simple sistema de prefijos

- H Para las señales del AHB

- S Para las señales del *ASB*

- P Para las señales del *APB*

- A Para las señales del AXI

- Por ejemplo HADDR[31:0] y PADDR[31:0] son las líneas de Address del AHB y APB respectivamente.

- En la implementaciones AXI el Bus de Address se separa para lectura y escritura, no obstante respeta las terminologías, siendo respectivamente ARADDR[31-0] y AWADDR[31-0]

Nombre Fuente Descripción

| Nombre            | Fuente          | Descripción                                                                                      |

|-------------------|-----------------|--------------------------------------------------------------------------------------------------|

| HCLK<br>Bus clock | Clock<br>source | Temporiza todas las transferencias. Todas las señales temporizan en el flanco ascendente de HCLK |

| Nombre            | Fuente                  | Descripción                                                                                      |

|-------------------|-------------------------|--------------------------------------------------------------------------------------------------|

| HCLK<br>Bus clock | Clock<br>source         | Temporiza todas las transferencias. Todas las señales temporizan en el flanco ascendente de HCLK |

| HRESETn Reset     | Controlador<br>de Reset | Señal activa Baja utilizada para resetear al sistema y al<br>Bus. Es la única señal activa Baja. |

| Nombre                      | Fuente                  | Descripción                                                                                      |

|-----------------------------|-------------------------|--------------------------------------------------------------------------------------------------|

| HCLK<br>Bus clock           | Clock<br>source         | Temporiza todas las transferencias. Todas las señales temporizan en el flanco ascendente de HCLK |

| HRESETn Reset               | Controlador<br>de Reset | Señal activa Baja utilizada para resetear al sistema y al<br>Bus. Es la única señal activa Baja. |

| HADDR [31:0]<br>Address bus | Master                  | Address bus de 32 bits del Sistema.                                                              |

| Nombre                     | Fuente               | Descripción                                                                                      |

|----------------------------|----------------------|--------------------------------------------------------------------------------------------------|

| HCLK<br>Bus clock          | Clock<br>source      | Temporiza todas las transferencias. Todas las señales temporizan en el flanco ascendente de HCLK |

| HRESETn Reset              | Controlador de Reset | Señal activa Baja utilizada para resetear al sistema y al<br>Bus. Es la única señal activa Baja. |

| HADDR[31:0]<br>Address bus | Master               | Address bus de 32 bits del Sistema.                                                              |

| HTRANS [1:0] Transfer type | Master               | Indica el tipo de transferencia en curso, que puede ser NONSEQUENTIAL, SEQUENTIAL, IDLE O BUSY.  |

| Nombre                     | Fuente               | Descripción                                                                                                    |

|----------------------------|----------------------|----------------------------------------------------------------------------------------------------------------|

| HCLK<br>Bus clock          | Clock<br>source      | Temporiza todas las transferencias. Todas las señales temporizan en el flanco ascendente de HCLK               |

| HRESETn Reset              | Controlador de Reset | Señal activa Baja utilizada para resetear al sistema y al<br>Bus. Es la única señal activa Baja.               |

| HADDR[31:0]<br>Address bus | Master               | Address bus de 32 bits del Sistema.                                                                            |

| HTRANS [1:0] Transfer type | Master               | Indica el tipo de transferencia en curso, que puede ser NONSEQUENTIAL, SEQUENTIAL, IDLE O BUSY.                |

| <b>HWRITE</b> Transfer dir | Master               | Cuando es Alta esta señal indica una transferencia de escritura y cuando es Baja una transferencia de lectura. |

| Nombre                      | Fuente               | Descripción                                                                                                                                                      |

|-----------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCLK<br>Bus clock           | Clock<br>source      | Temporiza todas las transferencias. Todas las señales temporizan en el flanco ascendente de HCLK                                                                 |

| HRESETn Reset               | Controlador de Reset | Señal activa Baja utilizada para resetear al sistema y al<br>Bus. Es la única señal activa Baja.                                                                 |

| HADDR[31:0]<br>Address bus  | Master               | Address bus de 32 bits del Sistema.                                                                                                                              |

| HTRANS [1:0] Transfer type  | Master               | Indica el tipo de transferencia en curso, que puede ser NONSEQUENTIAL, SEQUENTIAL, IDLE O BUSY.                                                                  |

| HWRITE<br>Transfer dir      | Master               | Cuando es Alta esta señal indica una transferencia de escritura y cuando es Baja una transferencia de lectura.                                                   |

| HSIZE[2:0]<br>Transfer size | Master               | Indica el tamaño de la transferencia: byte (8-bit), half-word (16-bit) o word (32-bit). El protocolo permite un máximo de 1024 bits, para transferencias largas. |

| Nombre                     | Fuente               | Descripción                                                                                                                                                          |

|----------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCLK<br>Bus clock          | Clock<br>source      | Temporiza todas las transferencias. Todas las señales temporizan en el flanco ascendente de HCLK                                                                     |

| HRESETn Reset              | Controlador de Reset | Señal activa Baja utilizada para resetear al sistema y al<br>Bus. Es la única señal activa Baja.                                                                     |

| HADDR[31:0]<br>Address bus | Master               | Address bus de 32 bits del Sistema.                                                                                                                                  |

| HTRANS [1:0] Transfer type | Master               | Indica el tipo de transferencia en curso, que puede ser NONSEQUENTIAL, SEQUENTIAL, IDLE O BUSY.                                                                      |

| HWRITE<br>Transfer dir     | Master               | Cuando es Alta esta señal indica una transferencia de escritura y cuando es Baja una transferencia de lectura.                                                       |

| HSIZE [2:0] Transfer size  | Master               | Indica el tamaño de la transferencia: byte (8-bit), half-word (16-bit) o word (32-bit). El protocolo permite un máximo de 1024 bits, para transferencias largas.     |

| HBURST [2:0] Burst type    | Master               | Indica si la transferencia forma parte de una ráfa-<br>ga (burst). Tamaños de burst soportados (beat<br>bursts): 4, 8 y 16. Y puede ser incremental o wrap-<br>ping. |

| Nombre                         | Fuente | Descripción                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPROT [3:0] Protection control | Master | Proveen información adicional del acceso al bus, estando en principio previstas para ser utilizadas por cualquier módulo que necesite implementar algún nivel de protección. Indican si la transferencia es un opcode fetch o un acceso a datos, como también si la transferencia se realiza en modo privilegiado o en modo usuario. Para Masters con MMU estas señales también indican si la dirección actual es cacheable o bufferable. |

| Nombre                          | Fuente | Descripción                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPROT [3:0] Protection control  | Master | Proveen información adicional del acceso al bus, estando en principio previstas para ser utilizadas por cualquier módulo que necesite implementar algún nivel de protección. Indican si la transferencia es un opcode fetch o un acceso a datos, como también si la transferencia se realiza en modo privilegiado o en modo usuario. Para Masters con MMU estas señales también indican si la dirección actual es cacheable o bufferable. |

| HWDATA [31:0]<br>Write data bus | Master | Se emplea para transferir datos desde el Master a los Slaves durante operaciones de escritura. Se recomiendo un ancho de bus mínimo de 32 bits. Este ancho puede ampliarse fácilmente para extender la operación a mayor ancho de banda.                                                                                                                                                                                                  |

| Nombre                          | Fuente  | Descripción                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPROT [3:0] Protection control  | Master  | Proveen información adicional del acceso al bus, estando en principio previstas para ser utilizadas por cualquier módulo que necesite implementar algún nivel de protección. Indican si la transferencia es un opcode fetch o un acceso a datos, como también si la transferencia se realiza en modo privilegiado o en modo usuario. Para Masters con MMU estas señales también indican si la dirección actual es cacheable o bufferable. |

| HWDATA [31:0]<br>Write data bus | Master  | Se emplea para transferir datos desde el Master a los Slaves durante operaciones de escritura. Se recomiendo un ancho de bus mínimo de 32 bits. Este ancho puede ampliarse fácilmente para extender la operación a mayor ancho de banda.                                                                                                                                                                                                  |

| HSEL×<br>Slave select           | Decoder | Cada Slave AHB tiene una señal de Chip Select que le indica que es el target de la transacción en curso. Esta señal se obtiene decodificando mediante lógica combinatoria las líneas de Address.                                                                                                                                                                                                                                          |

| Nombre       | Fuente | Descripción                                             |

|--------------|--------|---------------------------------------------------------|

| HRDATA[31:0] | Slave  | Es el camino de datos para transferencias desde un Sla- |

| Read data    |        | ve hacia los Masters durante operaciones de lectura. Se |

| bus          |        | recomiendo como mínimo 32 bits de ancho. Este ancho     |

|              |        | puede ampliarse fácilmente para extender la operación   |

|              |        | a mayor ancho de banda.                                 |

| Nombre                            | Fuente | Descripción                                                                                                                                                                                                                                     |

|-----------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HRDATA [31:0]<br>Read data<br>bus | Slave  | Es el camino de datos para transferencias desde un Slave hacia los Masters durante operaciones de lectura. Se recomiendo como mínimo 32 bits de ancho. Este ancho puede ampliarse fácilmente para extender la operación a mayor ancho de banda. |

| HREADY<br>Transfer done           | Slave  | Cuando HREADY va al estado Alto indica que la transferencia en el Bus terminó. Llevándola en estado BAJO se puede extender la transferencia. Nota: Los Slaves conectados al bus toman HREADY como señal de entrada y de salida.                 |

| Nombre                           | Fuente | Descripción                                                                                                                                                                                                                                     |

|----------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HRDATA[31:0]<br>Read data<br>bus | Slave  | Es el camino de datos para transferencias desde un Slave hacia los Masters durante operaciones de lectura. Se recomiendo como mínimo 32 bits de ancho. Este ancho puede ampliarse fácilmente para extender la operación a mayor ancho de banda. |

| HREADY<br>Transfer done          | Slave  | Cuando HREADY va al estado Alto indica que la trans-<br>ferencia en el Bus terminó. Llevándola en estado BAJO<br>se puede extender la transferencia. Nota: Los Slaves co-<br>nectados al bus toman HREADY como señal de entrada<br>y de salida. |

| HRESP [1:0] Transfer response    | Slave  | Proporciona información adicional del estado de la transferencia. Hay cuatro respuestas posibles: OKAY, ERROR, RETRY y SPLIT.                                                                                                                   |

| Nombre      | Fuente | Descripción                                             |

|-------------|--------|---------------------------------------------------------|

| HBUSREQx    | Master | Señal de un Master x al Árbitro de Bus para solicitarle |

| Bus Request |        | el Bus. El árbitro tiene una señal como ésta por cada   |

|             |        | Master. Máximo 16.                                      |

| Nombre                       | Fuente | Descripción                                                                                                                                                                                                     |

|------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HBUSREQx<br>Bus Request      | Master | Señal de un Master x al Árbitro de Bus para solicitarle el Bus. El árbitro tiene una señal como ésta por cada Master. Máximo 16.                                                                                |

| HLOCKx Loc-<br>ked Transfers | Master | Cuando va al estado Alto indica el Master requiere blo-<br>quear el acceso al bus a cualquier otro Master. Cual-<br>quier otro Master que solicite el bus tiene que esperar<br>que ésta línea tome estado BAJO. |

| Nombre                       | Fuente  | Descripción                                                                                                                                                                                                                                                                  |

|------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HBUSREQx<br>Bus Request      | Master  | Señal de un Master x al Árbitro de Bus para solicitarle el Bus. El árbitro tiene una señal como ésta por cada Master. Máximo 16.                                                                                                                                             |

| HLOCKx Loc-<br>ked Transfers | Master  | Cuando va al estado Alto indica el Master requiere blo-<br>quear el acceso al bus a cualquier otro Master. Cual-<br>quier otro Master que solicite el bus tiene que esperar<br>que ésta línea tome estado BAJO.                                                              |

| HGRANT* Bus<br>Grant         | Árbitro | Indica que el Master x del Bus es de todos el que mayor prioridad tienen a partir de este momento. La posesión de las líneas de Address y Control finaliza cuando se activa (Alta) HREADY. De modo que un Master consigue acceso al Bus cuando HGRANTX y HREADY están Altas. |

| Nombre                              | Fuente  | Descripción                                                                                                                                                                                                                                                                              |

|-------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HMASTER [3:0]<br>Master Num-<br>ber | Árbitro | Indica que Master de Bus está cursando la transferencia en el Bus. Es utilizada por los Slaves que soportan tipos de transferencias <b>SPLIT</b> para determinar que Master está intentando el acceso. El Timing de esta señal está alineado con el de las señales de Address y Control. |

| Nombre                              | Fuente  | Descripción                                                                                                                                                                                                                                                                              |

|-------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HMASTER [3:0]<br>Master Num-<br>ber | Árbitro | Indica que Master de Bus está cursando la transferencia en el Bus. Es utilizada por los Slaves que soportan tipos de transferencias <b>SPLIT</b> para determinar que Master está intentando el acceso. El Timing de esta señal está alineado con el de las señales de Address y Control. |

| HMASTLOCK<br>Locked se-<br>quence   | Árbitro | Indica que el Master actualmente en poder del Bus está cursando una transferencia con el bus lockeado. Tiene el mismo Timing que <b>HMASTLOCK</b>                                                                                                                                        |

| Nombre                                    | Fuente                  | Descripción                                                                                                                                                                                                                                                                              |

|-------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HMASTER [3:0]<br>Master Num-<br>ber       | Árbitro                 | Indica que Master de Bus está cursando la transferencia en el Bus. Es utilizada por los Slaves que soportan tipos de transferencias <b>SPLIT</b> para determinar que Master está intentando el acceso. El Timing de esta señal está alineado con el de las señales de Address y Control. |

| HMASTLOCK<br>Locked sequence              | Árbitro                 | Indica que el Master actualmente en poder del Bus está cursando una transferencia con el bus lockeado. Tiene el mismo Timing que <b>HMASTLOCK</b>                                                                                                                                        |

| HSPLITx [15:0<br>Split completion request | Slave<br>(con<br>SPLIT) | Este Bus de 16 bits sirve para que un Slave le indique al Árbitro cual de los Masters se debe rehabilitar para reintentar una transferencia <b>SPLIT</b> . Cada uno de estos bits identifica a uno de los Masters.                                                                       |

| Nombre            | Descripción                                                                                    |

|-------------------|------------------------------------------------------------------------------------------------|

| PCLK<br>Bus clock | El flanco ascendente de <b>PCLK</b> se usa para temporizar todas las transferencias sobre APB. |

| Nombre               | Descripción                                                                                                      |

|----------------------|------------------------------------------------------------------------------------------------------------------|

| PCLK<br>Bus clock    | El flanco ascendente de <b>PCLK</b> se usa para temporizar todas las transferencias sobre APB.                   |

| PRESETn<br>APB reset | La señal de reset del APB es activa Baja y normalmente se co-<br>necta directamente a la señal de Reset del bus. |

| Nombre                            | Descripción                                                                                                                |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| PCLK<br>Bus clock                 | El flanco ascendente de <b>PCLK</b> se usa para temporizar todas las transferencias sobre APB.                             |

| PRESETn<br>APB reset              | La señal de reset del APB es activa Baja y normalmente se co-<br>necta directamente a la señal de Reset del bus.           |

| PADDR[31:0]<br>APB address<br>bus | Es el Bus de Direcciones del APB, que puede tener hasta 32 bits de ancho y es manejado por la Unidad de Bridge con el AHB. |

| Nombre                            | Descripción                                                                                                                                                                                                                                                                                                               |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK<br>Bus clock                 | El flanco ascendente de PCLK se usa para temporizar todas las transferencias sobre APB.                                                                                                                                                                                                                                   |

| PRESETn<br>APB reset              | La señal de reset del APB es activa Baja y normalmente se co-<br>necta directamente a la señal de Reset del bus.                                                                                                                                                                                                          |

| PADDR[31:0]<br>APB address<br>bus | Es el Bus de Direcciones del APB, que puede tener hasta 32 bits de ancho y es manejado por la Unidad de Bridge con el AHB.                                                                                                                                                                                                |

| PSELX APB select                  | Es una señal desde cada decodificador secundario dentro de la Unidad de Bridge del Bus de Periféricos, hasta cada periférico Slave x del Bus. Esta señal indica al dispositivo Slave que ha sido seleccionado y que se requiere una transferencia de Datos. Debe haber una señal <b>PSELx</b> por cada dispositivo Slave. |

| Nombre     | Descripción                                                            |

|------------|------------------------------------------------------------------------|

| PENABLE    | Esta señal de strobe se emplea para temporizar todos los acce-         |

| APB strobe | sos sobre los periféricos del Bus. La señal de habilitación se utiliza |

|            | para indicar el inicio del segundo ciclo de una transferencia APB.     |

|            | El ciclo ascendente de <b>PENABLE</b> ocurre en el medio de una trans- |

|            | ferencia APB.                                                          |

| Nombre                     | Descripción                                                                                                                                                                                                                                                                               |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PENABLE<br>APB strobe      | Esta señal de strobe se emplea para temporizar todos los accesos sobre los periféricos del Bus. La señal de habilitación se utiliza para indicar el inicio del segundo ciclo de una transferencia APB. El ciclo ascendente de <b>PENABLE</b> ocurre en el medio de una transferencia APB. |

| PWRITE<br>APB transfer dir | Cuando es Alta, esta señal indica un acceso de escritura en el APE<br>y cuando es Baja un acceso de lectura.                                                                                                                                                                              |

| Nombre                     | Descripción                                                                                                                                                                                                                                                                               |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PENABLE<br>APB strobe      | Esta señal de strobe se emplea para temporizar todos los accesos sobre los periféricos del Bus. La señal de habilitación se utiliza para indicar el inicio del segundo ciclo de una transferencia APB. El ciclo ascendente de <b>PENABLE</b> ocurre en el medio de una transferencia APB. |

| PWRITE<br>APB transfer dir | Cuando es Alta, esta señal indica un acceso de escritura en el APB y cuando es Baja un acceso de lectura.                                                                                                                                                                                 |

| PRDATA APB read data bus   | El bus de datos de lectura es controlado por el Slave durante los ciclos de lectura (PWRITE Baja). El Bus de datos de lectura puede tener hasta 32 bits de ancho.                                                                                                                         |

| Nombre                     | Descripción                                                                                                                                                                                                                                                                               |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PENABLE<br>APB strobe      | Esta señal de strobe se emplea para temporizar todos los accesos sobre los periféricos del Bus. La señal de habilitación se utiliza para indicar el inicio del segundo ciclo de una transferencia APB. El ciclo ascendente de <b>PENABLE</b> ocurre en el medio de una transferencia APB. |

| PWRITE<br>APB transfer dir | Cuando es Alta, esta señal indica un acceso de escritura en el APB, y cuando es Baja un acceso de lectura.                                                                                                                                                                                |

| PRDATA APB read data bus   | El bus de datos de lectura es controlado por el Slave durante los ciclos de lectura (PWRITE Baja). El Bus de datos de lectura puede tener hasta 32 bits de ancho.                                                                                                                         |

| PWDATA APB write data bus  | El bus de datos de escritura es manejado por el Bridge del Bus de<br>Periféricos durante ciclos de escritura (PWRITE Alta). Este bus<br>puede tener hasta 32 bits de ancho.                                                                                                               |

#### **Temario**

- Vistazo General

- Bus AMBA

- Protocolos AMBA

- AMBA V2+

- Bus de Sistema de Alta performance

- Bus de Periféricos simples

- Lineamientos para organizar un Bus

- Señalización

- Funcionamiento y Operación

- 3 AX

- Características

## Sistema de Interconexión

### Sistema de Interconexión

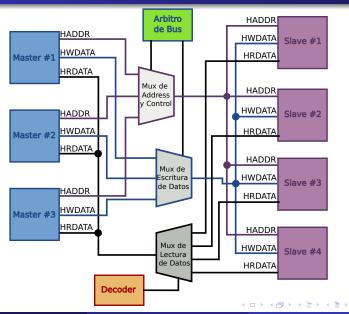

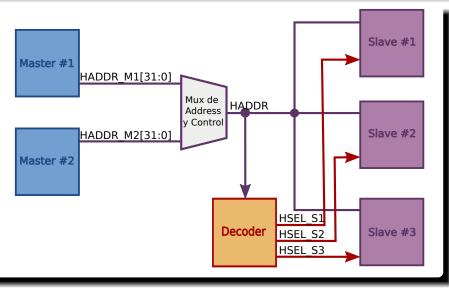

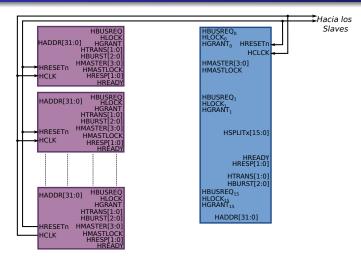

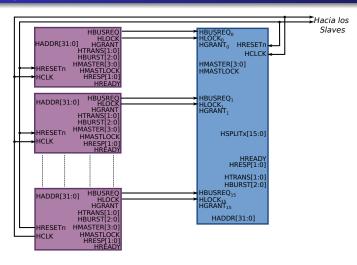

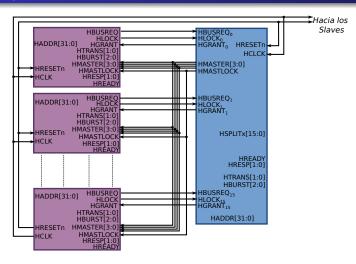

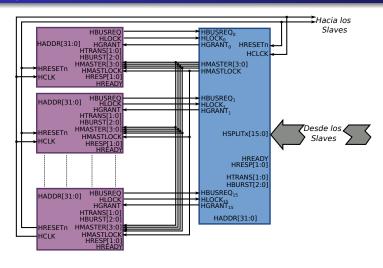

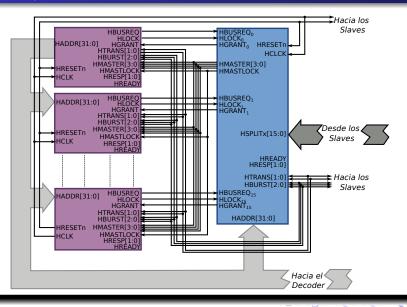

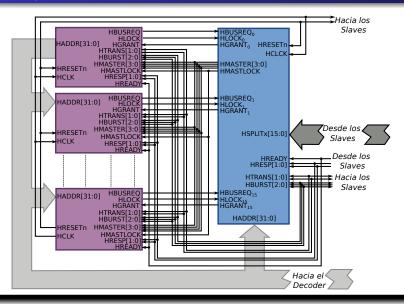

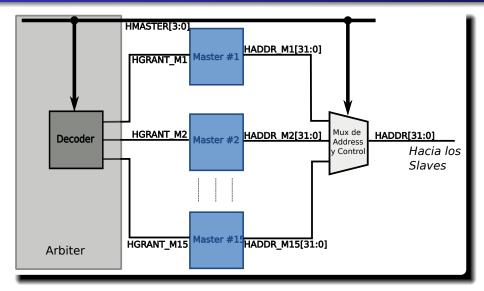

El protocolo AMBA AHB está pensado para funcionar en base a un esquema de interconexión basado en un Multiplexor centralizado.

## Sistema de Interconexión

- El protocolo AMBA AHB está pensado para funcionar en base a un esquema de interconexión basado en un Multiplexor centralizado.

- De tal modo que todos los Masters ponen sus señales de Address y Control indicando el tipo de transferencia que desean cursar.

#### Sistema de Interconexión

- El protocolo AMBA AHB está pensado para funcionar en base a un esquema de interconexión basado en un Multiplexor centralizado.

- De tal modo que todos los Masters ponen sus señales de Address y Control indicando el tipo de transferencia que desean cursar.

- Un Árbitro de bus selecciona el Bus de Address y Control de uno de los Master para rutearlo hacia los slaves.

### Sistema de Interconexión

- El protocolo AMBA AHB está pensado para funcionar en base a un esquema de interconexión basado en un Multiplexor centralizado.

- De tal modo que todos los Masters ponen sus señales de Address y Control indicando el tipo de transferencia que desean cursar.

- Un Árbitro de bus selecciona el Bus de Address y Control de uno de los Master para rutearlo hacia los slaves.

- Se requiere además de un decodificador centralizado que controle los datos leídos y las señales de respuesta del Multiplexor, que seleccionará las señales del Slave involucrado en la transferencia.

### Arquitectura detallada de AHB

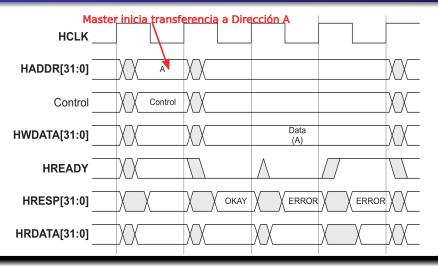

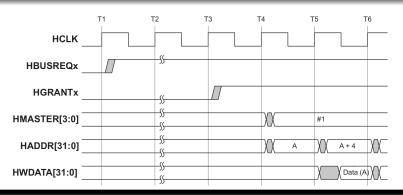

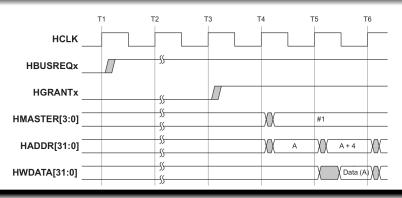

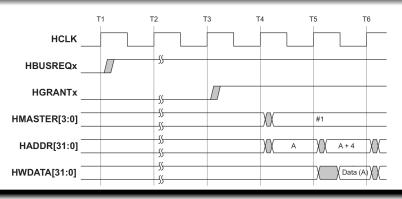

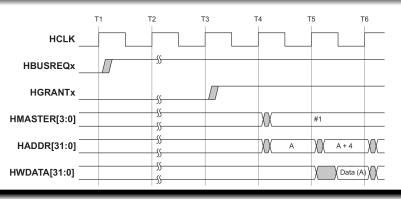

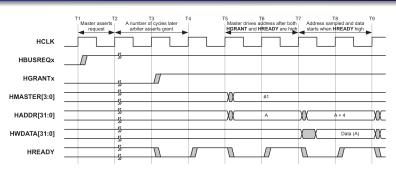

Un Master inicia una transferencia AHB, una vez que se le haya concedido el bus ("granted").

- Un Master inicia una transferencia AHB, una vez que se le haya concedido el bus ("granted").

- Cuando un Master necesita iniciar una transferencia, señaliza al Árbitro de Bus: Request

- Un Master inicia una transferencia AHB, una vez que se le haya concedido el bus ("granted").

- Cuando un Master necesita iniciar una transferencia, señaliza al Árbitro de Bus: Request

- El Árbitro le indica al Master cuando puede utilizar el bus: *Grant*.

Condición indispensable para inicio de una transferencia.

- Un Master inicia una transferencia AHB, una vez que se le haya concedido el bus ("granted").

- Cuando un Master necesita iniciar una transferencia, señaliza al Árbitro de Bus: Request

- El Árbitro le indica al Master cuando puede utilizar el bus: *Grant*.

Condición indispensable para inicio de una transferencia.

- El Master inicia la transferencia colocando en el Bus la información necesaria: dirección a la que necesita acceder, el sentido y el ancho de la transferencia, y si ésta forma parte de un Burst.

- Un Master inicia una transferencia AHB, una vez que se le haya concedido el bus ("granted").

- Cuando un Master necesita iniciar una transferencia, señaliza al Árbitro de Bus: Request

- El Árbitro le indica al Master cuando puede utilizar el bus: *Grant*.

Condición indispensable para inicio de una transferencia.

- El Master inicia la transferencia colocando en el Bus la información necesaria: dirección a la que necesita acceder, el sentido y el ancho de la transferencia, y si ésta forma parte de un Burst.

- Una transferencia Burst puede ser incremental o wrapping dependiendo de como opera al alcanzar la dirección límite.

Protocolos AMBA

- Un Master inicia una transferencia AHB, una vez que se le haya concedido el bus ("granted").

- Cuando un Master necesita iniciar una transferencia, señaliza al Árbitro de Bus: Request

- El Árbitro le indica al Master cuando puede utilizar el bus: Grant. Condición indispensable para inicio de una transferencia.

- El Master inicia la transferencia colocando en el Bus la información necesaria: dirección a la que necesita acceder, el sentido y el ancho de la transferencia, y si ésta forma parte de un Burst.

- Una transferencia Burst puede ser incremental o wrapping dependiendo de como opera al alcanzar la dirección límite.

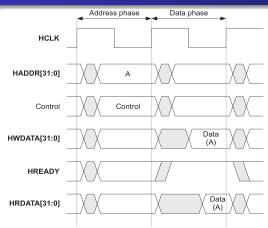

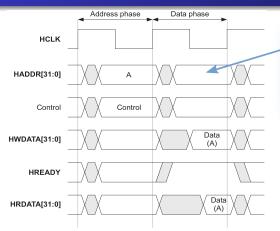

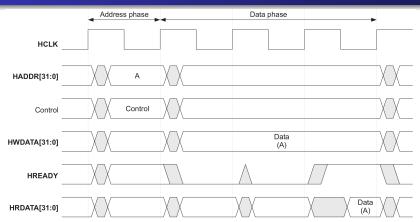

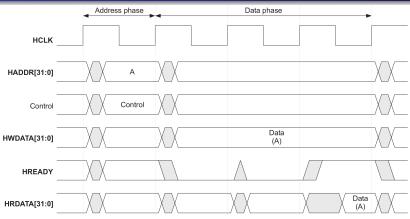

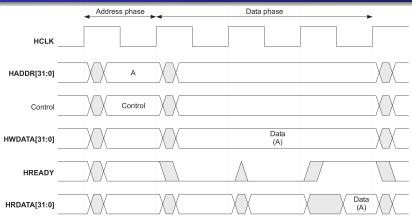

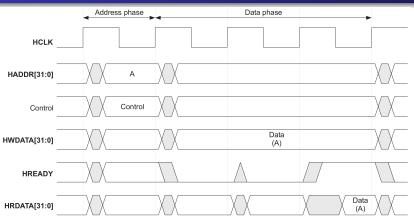

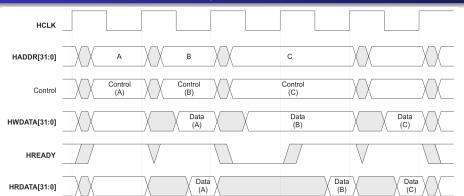

- Cada transferencia consiste de un ciclo de Address y Control, seguido de uno o mas ciclos de datos.

- Un Master inicia una transferencia AHB, una vez que se le haya concedido el bus ("granted").

- Cuando un Master necesita iniciar una transferencia, señaliza al Árbitro de Bus: Request

- El Árbitro le indica al Master cuando puede utilizar el bus: *Grant*.

Condición indispensable para inicio de una transferencia.

- El Master inicia la transferencia colocando en el Bus la información necesaria: dirección a la que necesita acceder, el sentido y el ancho de la transferencia, y si ésta forma parte de un Burst.

- Una transferencia Burst puede ser incremental o wrapping dependiendo de como opera al alcanzar la dirección límite.

- Cada transferencia consiste de un ciclo de Address y Control, seguido de uno o mas ciclos de datos.

- El ciclo de dirección no es extensible. Los slaves deben latchear la información de Address y Control.

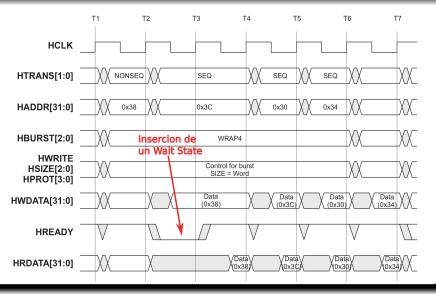

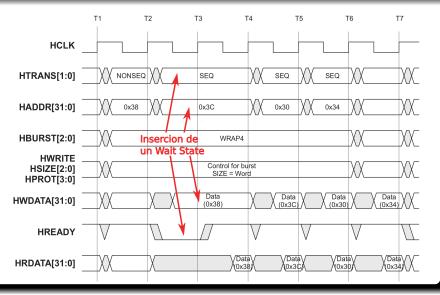

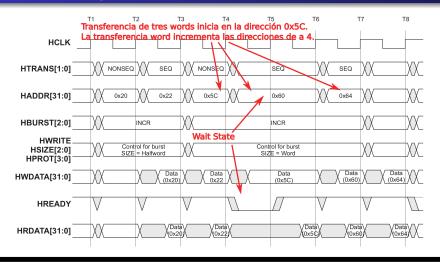

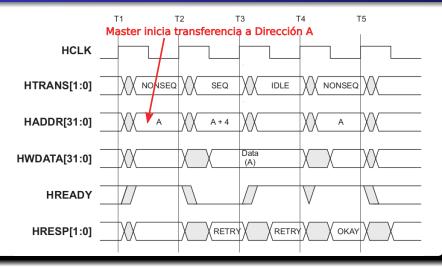

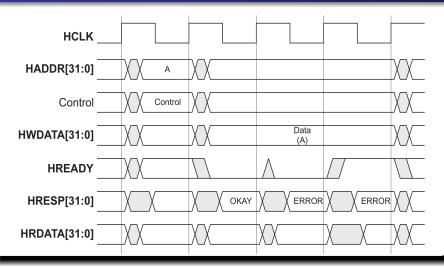

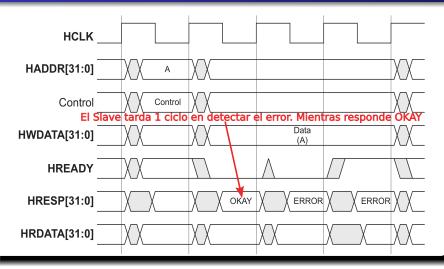

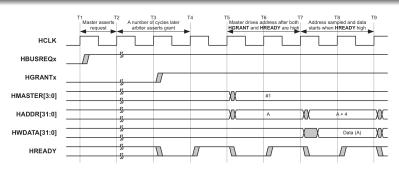

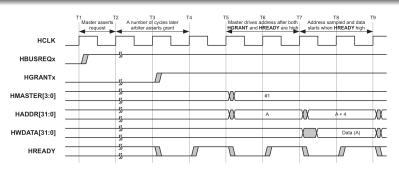

El ciclo de datos está sujeto a la señal HREADY. Mientras es Baja se insertan wait states.

- El ciclo de datos está sujeto a la señal HREADY. Mientras es Baja se insertan wait states.

- El Slave utiliza el par de líneas de respuesta HRESP[1:0], para indicar el estado o resultado de la transferencia:

- El ciclo de datos está sujeto a la señal HREADY. Mientras es Baja se insertan wait states.

- El Slave utiliza el par de líneas de respuesta HRESP[1:0], para indicar el estado o resultado de la transferencia:

- OKAY La transferencia se cursa con normalidad. Cuando **HREADY** tome estado alto finalizará exitosamente.

- El ciclo de datos está sujeto a la señal HREADY. Mientras es Baja se insertan wait states.

- El Slave utiliza el par de líneas de respuesta HRESP[1:0], para indicar el estado o resultado de la transferencia:

- OKAY La transferencia se cursa con normalidad. Cuando **HREADY** tome estado alto finalizará exitosamente.

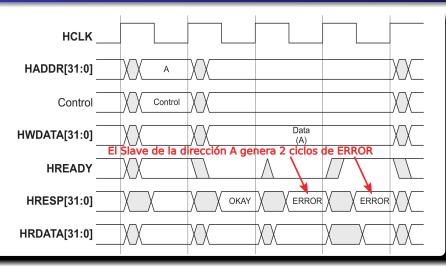

ERROR Indica error en la transferencia.

- El ciclo de datos está sujeto a la señal HREADY. Mientras es Baja se insertan wait states.

- El Slave utiliza el par de líneas de respuesta HRESP[1:0], para indicar el estado o resultado de la transferencia:

- OKAY La transferencia se cursa con normalidad. Cuando **HREADY** tome estado alto finalizará exitosamente.

- ERROR Indica error en la transferencia.

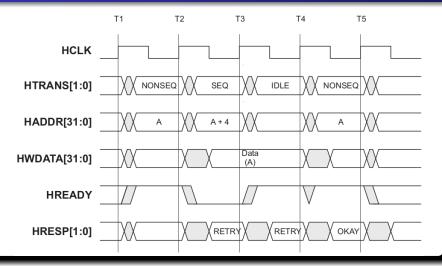

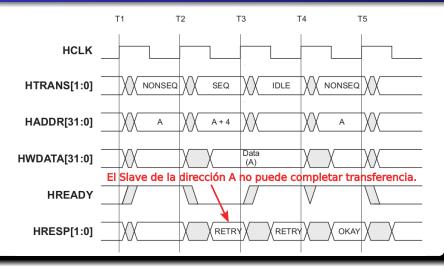

- RETRY La transferencia no puede completarse de manera inmediata, pero el Master debe reintentarla.

- El ciclo de datos está sujeto a la señal HREADY. Mientras es Baja se insertan wait states.

- El Slave utiliza el par de líneas de respuesta HRESP[1:0], para indicar el estado o resultado de la transferencia:

- OKAY La transferencia se cursa con normalidad. Cuando **HREADY** tome estado alto finalizará exitosamente.

- ERROR Indica error en la transferencia.

- RETRY La transferencia no puede completarse de manera inmediata, pero el Master debe reintentarla.

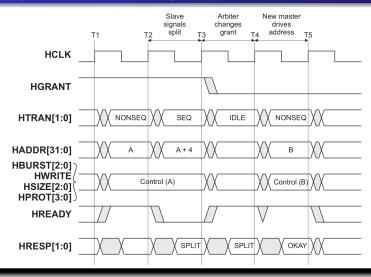

- SPLIT Es similar a **RETRY**.

- El ciclo de datos está sujeto a la señal HREADY. Mientras es Baja se insertan wait states.

- El Slave utiliza el par de líneas de respuesta HRESP[1:0], para indicar el estado o resultado de la transferencia:

- OKAY La transferencia se cursa con normalidad. Cuando **HREADY** tome estado alto finalizará exitosamente.

- ERROR Indica error en la transferencia.

- RETRY La transferencia no puede completarse de manera inmediata, pero el Master debe reintentarla.

- SPLIT Es similar a **RETRY**.

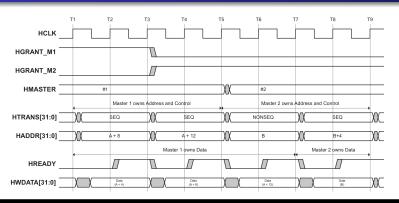

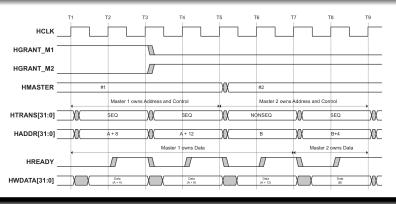

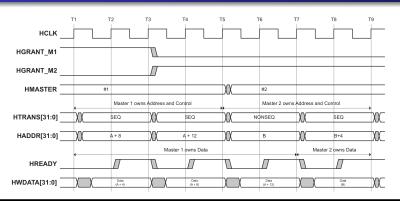

- Lo normal es que una transferencia Burst se complete antes de que el Árbitro de Bus habilite a otro Master.

- El ciclo de datos está sujeto a la señal HREADY. Mientras es Baja se insertan wait states.

- El Slave utiliza el par de líneas de respuesta HRESP[1:0], para indicar el estado o resultado de la transferencia:

- OKAY La transferencia se cursa con normalidad. Cuando **HREADY** tome estado alto finalizará exitosamente.

- ERROR Indica error en la transferencia.

- RETRY La transferencia no puede completarse de manera inmediata, pero el Master debe reintentarla.

- SPLIT Es similar a RETRY.

- Lo normal es que una transferencia Burst se complete antes de que el Árbitro de Bus habilite a otro Master.

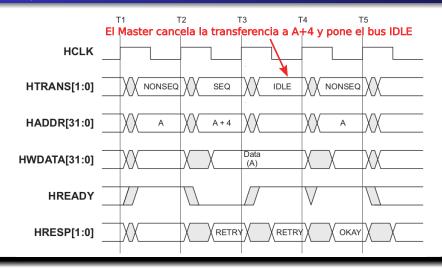

- En ocasiones para evitar demoras el Árbitro puede ordenar a un Master que interrumpa una transferencia Burst.

- El ciclo de datos está sujeto a la señal HREADY. Mientras es Baja se insertan wait states.

- El Slave utiliza el par de líneas de respuesta HRESP[1:0], para indicar el estado o resultado de la transferencia:

- OKAY La transferencia se cursa con normalidad. Cuando **HREADY** tome estado alto finalizará exitosamente.

- ERROR Indica error en la transferencia.

- RETRY La transferencia no puede completarse de manera inmediata, pero el Master debe reintentarla.

- SPLIT Es similar a **RETRY**.

- Lo normal es que una transferencia Burst se complete antes de que el Árbitro de Bus habilite a otro Master.

- En ocasiones para evitar demoras el Árbitro puede ordenar a un Master que interrumpa una transferencia Burst.

- El Master deberá rearbitrar la transferencia a posteriori.

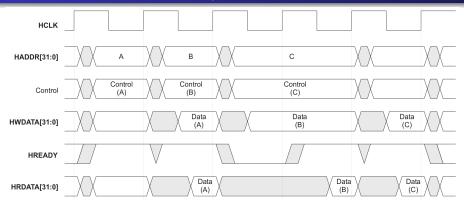

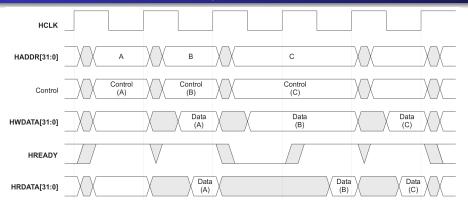

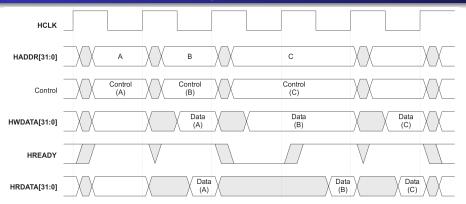

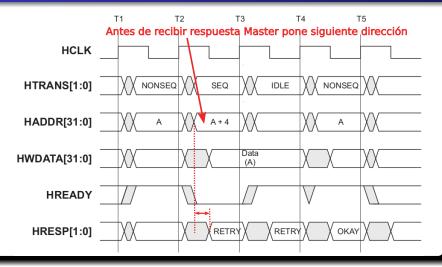

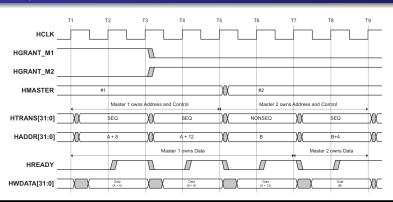

Durante la fase de datos de la transferencia en curso, se coloca la información de Address y Control de la próxima transferencia.

Durante la fase de datos de la transferencia en curso, se coloca la información de Address y Control de la próxima transferencia.

Este solapamiento de fases constituye la naturaleza pipeline del bus lo cual aumenta notablemente su rendimiento, sin requerir mas velocidad del Slave

Durante la fase de datos de la transferencia en curso, se coloca la información de Address y Control de la próxima transferencia.

Este solapamiento de fases constituye la naturaleza pipeline del bus lo cual aumenta notablemente su rendimiento, sin requerir mas velocidad del Slave

El ciclo de Address / Control siempre dura un ciclo de HCLCK.

Durante la fase de datos de la transferencia en curso, se coloca la información de Address y Control de la próxima transferencia.

Este solapamiento de fases constituye la naturaleza pipeline del bus lo cual aumenta notablemente su rendimiento, sin requerir mas velocidad del Slave

El ciclo de Address / Control siempre dura un ciclo de HCLCK. El Slave samplea siempre en el flanco ascendente de HCLCK.

√ Si el Slave requiere mas tiempo para responder, tiene la señal HREADY

✓ Si el Slave requiere mas tiempo para responder, tiene la señal **HREADY** ✓ Si la transferencia es de escritura el Master debe sostener los datos válidos en el bus durante los ciclos extendidos.

√ Si el Slave requiere mas tiempo para responder, tiene la señal HREADY √ Si la transferencia es de escritura el Master debe sostener los datos válidos en el bus durante los ciclos extendidos.

√Si es de Lectura, el Slave no proveerá datos válidos hasta que se active HREADY.

✓ Las transferencias a direcciones A y C son 0 wait states .

- $\checkmark$  Las transferencias a direcciones A y C son 0 wait states .

- ✓ La transferencia a la dirección B inserta un wait states .

- √ Las transferencias a direcciones A y C son 0 wait states.

- ✓ La transferencia a la dirección B inserta un wait states .

- ✓ Extender la fase de datos de la transferencia a la dirección B, genera demora en la fase de Address de la transferencia a la dirección C.

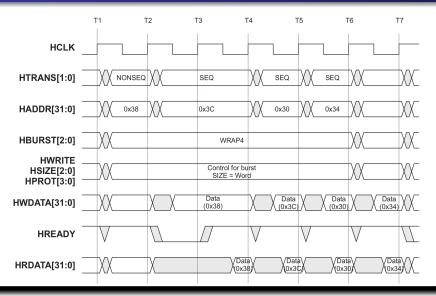

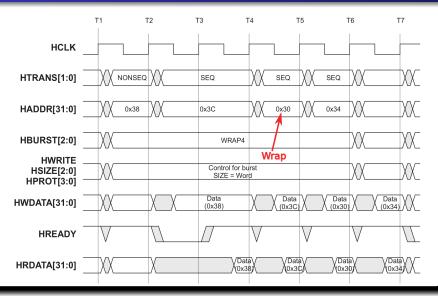

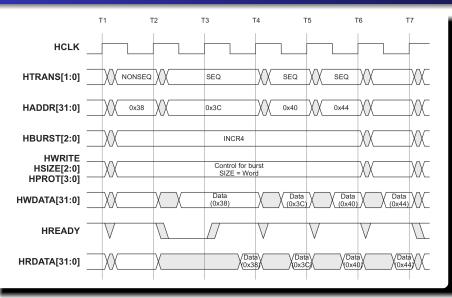

# Operación Burst

# Operación Burst

• Ráfagas de 4, 8 o 16 beats, y user-defined de hasta 1024 bytes.

# Operación Burst

- Ráfagas de 4, 8 o 16 beats, y user-defined de hasta 1024 bytes.

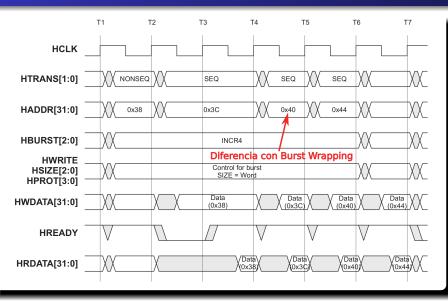

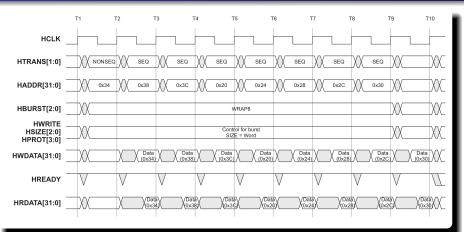

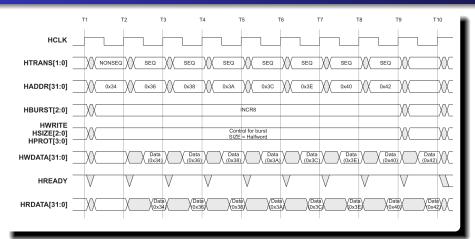

- En modo Incremental se accede a un área contigua de direccionamiento en donde cada dirección se obtiene incrementando la anterior.

- Ráfagas de 4, 8 o 16 beats, y user-defined de hasta 1024 bytes.

- En modo Incremental se accede a un área contigua de direccionamiento en donde cada dirección se obtiene incrementando la anterior.

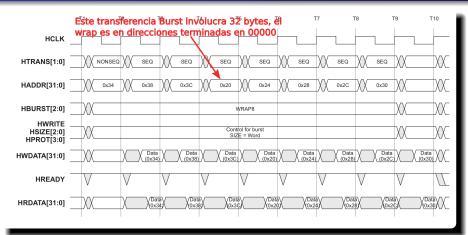

- En modo Wrapping si los datos no comienzan en direcciones alineadas, la transferencia es por la cantidad de beats.

- Ráfagas de 4, 8 o 16 beats, y user-defined de hasta 1024 bytes.

- En modo Incremental se accede a un área contigua de direccionamiento en donde cada dirección se obtiene incrementando la anterior.

- En modo Wrapping si los datos no comienzan en direcciones alineadas, la transferencia es por la cantidad de beats.

- Por lo tanto el wrap se produce al alcanzarse la dirección tope en cantidad de bytes del burst.

- Ráfagas de 4, 8 o 16 beats, y user-defined de hasta 1024 bytes.

- En modo Incremental se accede a un área contigua de direccionamiento en donde cada dirección se obtiene incrementando la anterior.

- En modo Wrapping si los datos no comienzan en direcciones alineadas, la transferencia es por la cantidad de beats.

- Por lo tanto el wrap se produce al alcanzarse la dirección tope en cantidad de bytes del burst.

- En una transferencia burst wrapping de 4 beats de acceso word, constará de 16 bytes en total. El wrapping se produce en la dirección múltiplo de 16 bytes.

- Ráfagas de 4, 8 o 16 beats, y user-defined de hasta 1024 bytes.

- En modo Incremental se accede a un área contigua de direccionamiento en donde cada dirección se obtiene incrementando la anterior.

- En modo Wrapping si los datos no comienzan en direcciones alineadas, la transferencia es por la cantidad de beats.

- Por lo tanto el wrap se produce al alcanzarse la dirección tope en cantidad de bytes del burst.

- En una transferencia burst wrapping de 4 beats de acceso word, constará de 16 bytes en total. El wrapping se produce en la dirección múltiplo de 16 bytes.

- Ejemplo: Si ésta transferencia comienza en la dirección 0x38, entonces son cuatro transferencias en las siguientes direcciones: 0x38, 0x3C, 0x30, 0x34.

### Codificación de tipos de Burst

| HBURST[2:0] | Tipo   | Descripción                              |

|-------------|--------|------------------------------------------|

| 000         | SINGLE | Single transfer                          |

| 001         | INCR   | Incrementing burst of unspecified length |

| 010         | WRAP4  | 4-beat wrapping burst                    |

| 011         | INCR4  | 4-beat incrementing burst                |

| 100         | WRAP8  | 8-beat wrapping burst                    |

| 101         | INCR8  | 8-beat incrementing burst                |

| 110         | WRAP16 | 16-beat wrapping burst                   |

| 111         | INCR16 | 16-beat incrementing burst               |

El límite máximo de una transferencia Burst es 1 Kbyte. Si en un burst incremental se trabaja con el tipo no especificado debe cuidarse de no superar este límite.

Las transferencias dentro de un burst deben estar alineadas acorde al tamaño del dato básico que se transmite.

✓ Bajo ciertas condiciones, una transferencia burst puede ser suspendida.

- $\checkmark$  Bajo ciertas condiciones, una transferencia burst puede ser suspendida.

- ✓ El Slave involucrado debe tener notificación inmediata.

- $\checkmark$  Bajo ciertas condiciones, una transferencia burst puede ser suspendida.

- ✓ El Slave involucrado debe tener notificación inmediata.

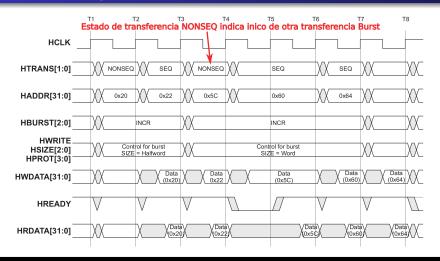

- √La información que un Slave debe monitorear es el estado de las Líneas HTRANS [1:0]. Si desde el inicio de la transacción el estado es BUSY o SEQUENTIAL la transacción burst prosigue normalmente.

- $\checkmark$  Bajo ciertas condiciones, una transferencia burst puede ser suspendida.

- ✓ El Slave involucrado debe tener notificación inmediata.

- ✓ La información que un Slave debe monitorear es el estado de las Líneas HTRANS [1:0]. Si desde el inicio de la transacción el estado es BUSY o SEQUENTIAL la transacción burst prosique normalmente.

- √ Si detecta el estado **NONSEQUENTIAL** o **IDLE**, significa que se ha iniciado una nueva transferencia burst, y que la anterior ha sido terminada.

- $\checkmark$  Bajo ciertas condiciones, una transferencia burst puede ser suspendida.

- ✓ El Slave involucrado debe tener notificación inmediata.

- √La información que un Slave debe monitorear es el estado de las Líneas HTRANS [1:0]. Si desde el inicio de la transacción el estado es BUSY o SEQUENTIAL la transacción burst prosigue normalmente.

- √Si detecta el estado **NONSEQUENTIAL** o **IDLE**, significa que se ha iniciado una nueva transferencia burst, y que la anterior ha sido terminada.

- √El Master que no logró completar la transferencia burst por haber perdido el control del Bus, deberá completarla cuando logre recuperar el bus. Para ello normalmente se inicia una transferencia de tamaño Undefined que curse los restantes *beats* que quedaron pendientes en la transferencia suspendida.

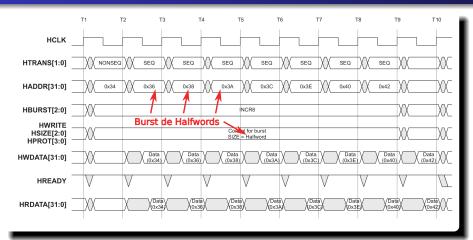

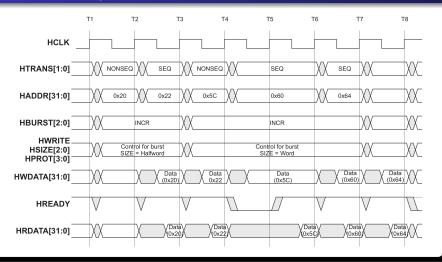

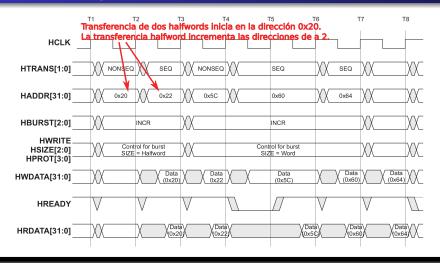

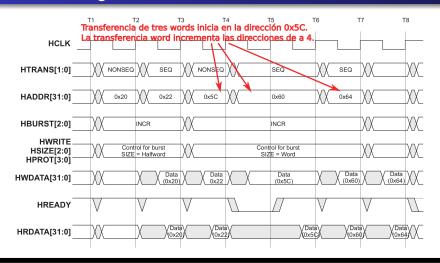

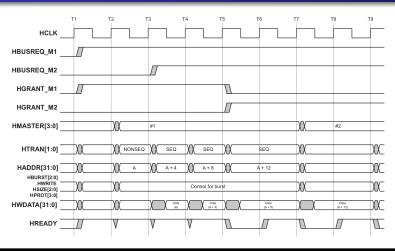

#### Burst Incremental de 4 beats

#### Burst Incremental de 4 beats

#### Burst Incremental de 8 beats

#### Burst Incremental de 8 beats

HWRITE: Si es Alta indica una transferencia de escritura. El Master debe colocar en HWDATA[31:0] la word a enviar al Slave seleccionado. Si es Baja la transferencia es de Lectura y el Slave deberá generar los datos en HRDATA[31:0]

- HWRITE: Si es Alta indica una transferencia de escritura. El Master debe colocar en HWDATA[31:0] la word a enviar al Slave seleccionado. Si es Baja la transferencia es de Lectura y el Slave deberá generar los datos en HRDATA[31:0]

- HSIZE[2:0]: Tamaño de la transferencia

- HWRITE: Si es Alta indica una transferencia de escritura. El Master debe colocar en HWDATA[31:0] la word a enviar al Slave seleccionado. Si es Baja la transferencia es de Lectura y el Slave deberá generar los datos en HRDATA[31:0]

- HSIZE[2:0]: Tamaño de la transferencia

| HSIZE[2] | HSIZE[1] | HSIZE[0] | Tamaño    | Descripción |

|----------|----------|----------|-----------|-------------|

| 0        | 0        | 0        | 8 bits    | Byte        |

| 0        | 0        | 1        | 16 bits   | Half Word   |

| 0        | 1        | 0        | 32 bits   | Word        |

| 0        | 1        | 1        | 64 bits   | -           |

| 1        | 0        | 0        | 128 bits  | 4-word line |

| 1        | 0        | 1        | 256 bits  | 8-word line |

| 1        | 1        | 0        | 512 bits  | -           |

| 1        | 1        | 1        | 1024 bits | -           |

HSIZE[2:0] junto con HBURST[2:0] determinan la dirección límite para transferencias Burst Wrapping.

- HSIZE[2:0] junto con HBURST[2:0] determinan la dirección límite para transferencias Burst Wrapping.

- HPROT [3:0]: Provee información acerca del destino del acceso al bus. Para procesadores con MMU provee información importante para implementar cierto nivel de protección. No se recomienda el uso en Slaves.

- HSIZE[2:0] junto con HBURST[2:0] determinan la dirección límite para transferencias Burst Wrapping.

- HPROT [3:0]: Provee información acerca del destino del acceso al bus. Para procesadores con MMU provee información importante para implementar cierto nivel de protección. No se recomienda el uso en Slaves.

| HPROT[3]<br>Cacheable | HPROT[2]<br>Buffereable | HPROT[1]<br>Priviedged | HPROT[0]<br>Data/Opcode | Descripción        |

|-----------------------|-------------------------|------------------------|-------------------------|--------------------|

| -                     | -                       | -                      | 0                       | Opcode Fetch       |

| -                     | -                       | -                      | 1                       | Data Access        |

| -                     | -                       | 0                      | -                       | User Access        |

| -                     | -                       | 1                      | -                       | Priviledged Access |

| -                     | 0                       | -                      | -                       | Not Buffereable    |

| -                     | 1                       | -                      | -                       | Buffereable        |

| 0                     | -                       | -                      | -                       | Not Cacheable      |

| 1                     | -                       | -                      | -                       | Cacheable          |

|                       |                         |                        | 4 □ → 4 €               |                    |

#### Decodificación de Direcciones

#### Decodificación de Direcciones

#### Decodificación de Direcciones

• El espacio mínimo que debe ocupar un Slave es 1 KByte.

- El espacio mínimo que debe ocupar un Slave es 1 KByte.

- Los Bus Masters deben diseñarse de modo de no realizar transferencias incrementales de mas de 1 KByte y así nunca traspasar el límite de direccionamiento de un Slave.

- El espacio mínimo que debe ocupar un Slave es 1 KByte.

- Los Bus Masters deben diseñarse de modo de no realizar transferencias incrementales de mas de 1 KByte y así nunca traspasar el límite de direccionamiento de un Slave.

- Si un Slave no llena el Kbyte de direccionamiento se puede implementar un Slave default que responda adecuadamente para aquellas direcciones no implementadas en el original, a saber:

- El espacio mínimo que debe ocupar un Slave es 1 KByte.

- Los Bus Masters deben diseñarse de modo de no realizar transferencias incrementales de mas de 1 KByte y así nunca traspasar el límite de direccionamiento de un Slave.

- Si un Slave no llena el Kbyte de direccionamiento se puede implementar un Slave default que responda adecuadamente para aquellas direcciones no implementadas en el original, a saber:

- Si se intentan transferencias NONSEQUENTIAL o SEQUENTIAL a una dirección inexistente el Slave default debe proveer respuesta ERROR.

- El espacio mínimo que debe ocupar un Slave es 1 KByte.

- Los Bus Masters deben diseñarse de modo de no realizar transferencias incrementales de mas de 1 KByte y así nunca traspasar el límite de direccionamiento de un Slave.

- Si un Slave no llena el Kbyte de direccionamiento se puede implementar un Slave default que responda adecuadamente para aquellas direcciones no implementadas en el original, a saber:

- Si se intentan transferencias NONSEQUENTIAL o SEQUENTIAL a una dirección inexistente el Slave default debe proveer respuesta ERROR.

- Por su parte, transferencias IDLE o BUSY a direcciones inexistentes deben generar una respuesta OKAY con 0 wait states.

- El espacio mínimo que debe ocupar un Slave es 1 KByte.

- Los Bus Masters deben diseñarse de modo de no realizar transferencias incrementales de mas de 1 KByte y así nunca traspasar el límite de direccionamiento de un Slave.