#### **ARM**

- Advanced RISC Machines Ltd.

- Compañía inglesa Dedicada al desarrollo de procesadores RISC, software y tecnologías relacionadas, fundada en 1990 por Apple Computer, Acorn Computer Group y VLSI Technology.

- Cubre aprox. el 75 % del mercado mundial en microcontroladores RISC

- Costos actuales (a igualdad de prestaciones) inferior a 8051.

TDII - Microcontroladores - ARM

•

#### **ARM**

En la actualidad, ARM Ltd no hace procesadores, solo los diseña y licencia sus diseños a fabricantes (P. ej: Analog Devices, Atmel, Cirrus Logic, Hyundai, Intel, Oki, Plilips, Samsung, Sharp, Lucent, 3Comp, HP, IBM, Sony, etc.).

TDII - Microcontroladores - ARM

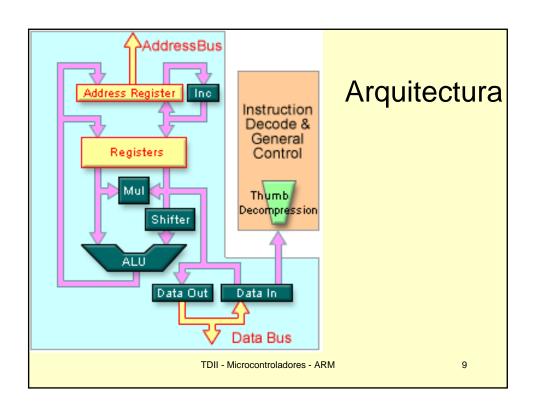

#### Características

- Computadora de 3 direcciones (registros) de 32 bits

- Single clock machines cycles

- Extensión Thumb

- Excepciones vectorizadas

- Número de transistores: > 74,209 implica bajo consumo.

- Frecuencias de operación: 45 133 MHz.

- Bus de 32 bits para datos e instrucciones.

- Elevado rendimiento: hasta 120 MIPS.

- Elevada densidad de código (Diseñado para trabajar en C)

TDII - Microcontroladores - ARM

3

#### Características

- Se basa en Arquitectura RISC.

- 37 registros de 32 bits (16 disponibles).

- Registros 0 a 7 disponibles en todo momento

- Memoria caché (dependiendo de la aplicación)

- Estructura del bus tipo Von Neuman (ARM7), tipo Harvard (ARM9)

TDII - Microcontroladores - ARM

#### **ARM**

- Tipos de datos de 8/16/32 bits

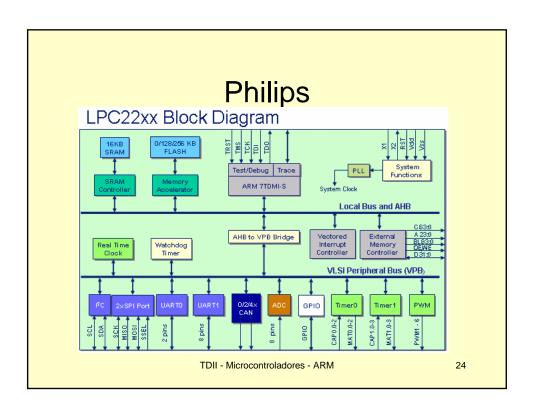

- 6 modos de operación: usr y sys, fiq, irq, svc, abt, sys, und.

- Todos las familias de procesadores ARM comparten el mismo conjunto de instrucciones

TDII - Microcontroladores - ARM

5

#### Risc

- Instrucciones de Procesamiento de datos

- Instrucciones de Transferencia de Datos

- Instrucciones de Control de Flujo

TDII - Microcontroladores - ARM

#### **RISC**

- Instrucciones conceptualmente simples.

- Transferencias Memoria/Registros exclusivamente LOAD/STORES.

- Las operaciones aritméticas son entre registros.

- Tamaño de instrucciones uniformes.

- Pocos formatos para las instrucciones.

- Conjunto de instrucciones ortogonal: poco o ningún traslape en la funcionalidad de las instrucciones.

- Pocos modos de direccionamiento.

TDII - Microcontroladores - ARM

7

#### Risc

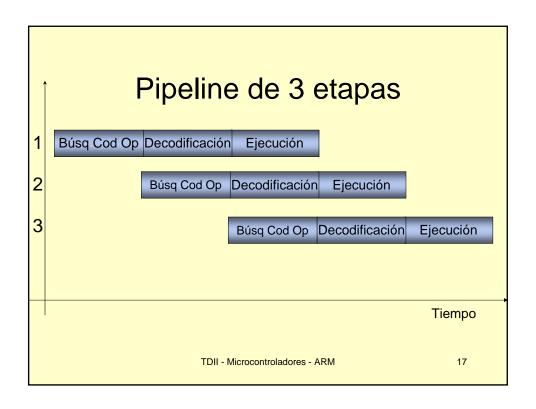

- Casi todas las instrucciones se ejecutan en un ciclo de reloj.

- Tendencia a tener un gran número de registros.

- Arquitectura RISC predomina en los procesadores de elevado rendimiento.

TDII - Microcontroladores - ARM

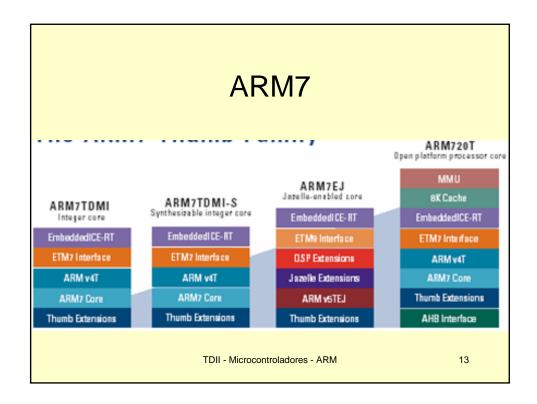

#### ARM7

- Alimentación: 3.3 V y 5 V.

- Bajo consumo de potencia: 80 mW.

- Tecnología CMOS.

- Extensiones: Thumb, Jazelle.

- Los miembros de ARM7 tienen un coprocesador de interfaz que permite la conexión hasta con 16 coprocesadores más.

TDII - Microcontroladores - ARM

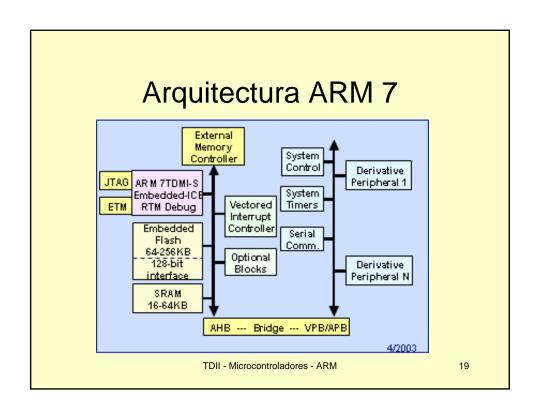

#### **ARM7TDMI**

- Es la versión mas utilizada de ARM7.

- ¿ TDMI ?

- T: "Thumb", soporta esta extensión.

- D: "Debug-interface".

- M: "Multiplier", hardware multiplicador.

- I: "Interrupt", interrupciones veloces.

TDII - Microcontroladores - ARM

#### **ARM7TDMI**

- Arquitectura de bus unificada.

- Lógica de depuración EmbeddedICE-RT.

- Interface ETM (Embedded Trace Macrocell).

TDII - Microcontroladores - ARM

15

# ARM7TDMI TOTAL Microcontroladores - ARM ARM7TDMI

#### ARM7EJ-S

- Versión sintetizable, incorpora las bondades del ARM7TDMI.

- Soporta ejecución acelerada de Java y operaciones DSP.

- Emplea tecnología ARM Jazelle.

TDII - Microcontroladores - ARM

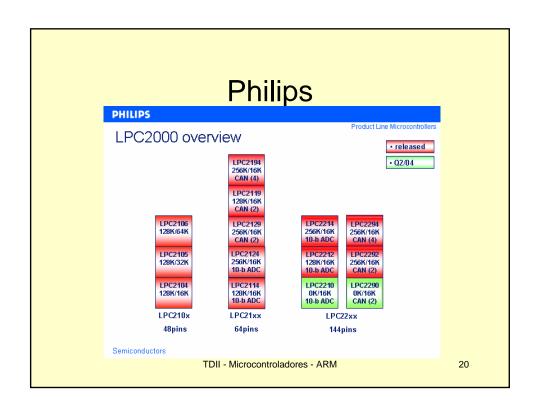

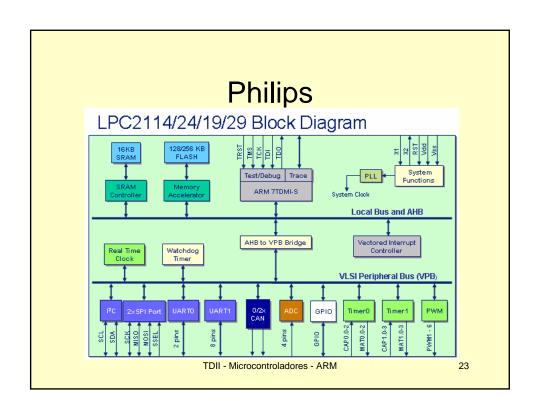

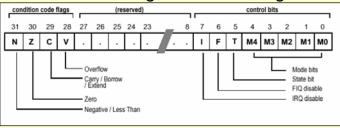

#### LPC22xx

- Núcleo a 1,8 V

- E/S a 3,3 V compatible TTL

- Icc = 35 mA

- Idle = 20 mA

- Sleep = 25 μA

TDII - Microcontroladores - ARM

25

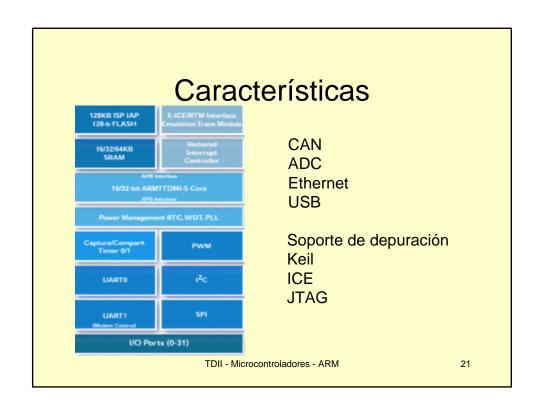

#### Características

- 3 tipos de Interrupciones

- FIQ

- Vectorizadas

- Interrupciones Generales

- 32 entradas de interrupción

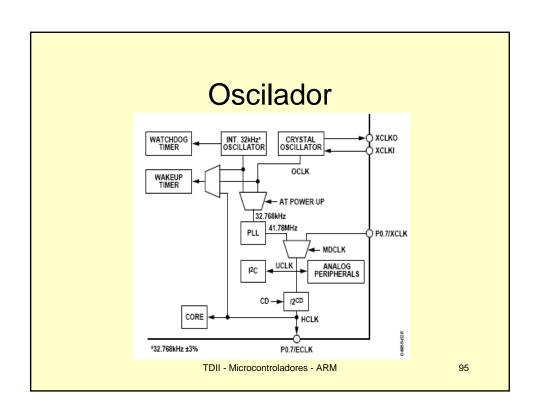

- PLL

- Frec in = 10 25 MHz

- Trabaja hasta 60 MHz

TDII - Microcontroladores - ARM

# Comunicación Serie

- SPI

- Hasta 2 canales que admiten master-slave

- Veloc = 1/8 clock

- UART

- 16550 compatible (con FIFO y flag de fifo llena).

- Velocidad hasta 1/16 del clock

TDII - Microcontroladores - ARM

27

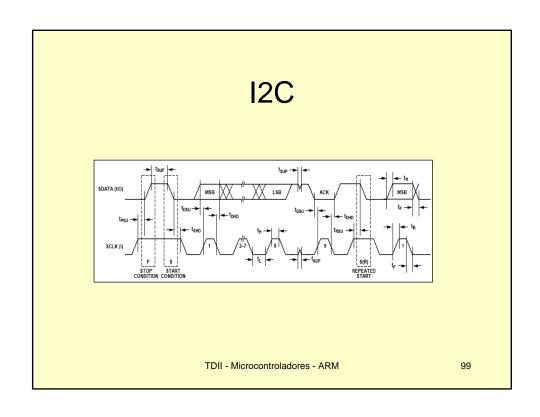

#### Comunicación Serie

- I2C

- Hasta 750 kHz con 7 bits de direccionamiento

- Bidireccional

- Sin Maestro (multimaster)

- CAN

TDII - Microcontroladores - ARM

# **Timers**

- De 32 bits con 4 registros de captura

- De 32 bits con 4 registros de coincidencia

- Watchdog que para debug no resetea al micro sino que genera excepciones

TDII - Microcontroladores - ARM

29

#### E/S

- 10 bits 0 a 3 V y 400 kmuestras/s

- 4 8 canales

- PWM de 32 bits con timer específico

- RTC

- 32 bits de E/S

TDII - Microcontroladores - ARM

#### ARM7

- Para sistemas que requieren manejo completo de memoria virtual y espacios de ejecución protegidos.

- Memoria caché de 8K

- MMU: unidad controladora de memoria.

- Para aplicaciones de plataforma abierta como Windows CE, Linux, Palm OS y Symbian OS.

TDII - Microcontroladores - ARM

31

#### MODOS DE OPERACIÓN ARM7.

- User (usr): estado normal de ejecución de programas

- FIQ (fiq): estado para transferencias de datos ( fast irq, transferencias tipo DMA)

- IRQ (irg): para dar servivicio a interrupciones generales

- Supervisor (svc): modo protegido para soporte del sistema operativo

- Abort mode (abt): usado cuando se aborta el ciclo fetch de datos o instrucciones.

- Undefined (und): usado cuando una instrucción indefinida es traida.

TDII - Microcontroladores - ARM

- Comparación

- CMP r1,r2

- CMN r1,r2

- TST r1,r2

- TEQ r1,r2

TDII - Microcontroladores - ARM

33

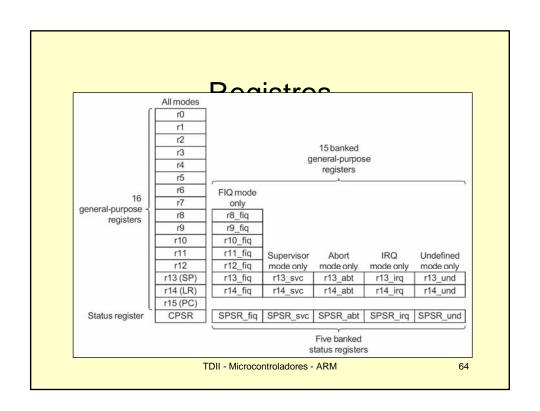

#### **REGISTROS ARM7.**

- 37 registros de 32 bits, 31 propósito general y 6 registros de estado.

- El número de registros disponibles y su estructura dependen del modo de operación

- 16 registros directamente accesibles (R0 R15).

- R13: puntero de pila (sp)

- R14: enlace a subrutina (Ir)

- Guarda el valor de R15 cuando se ejecuta una instrucción BL

TDII - Microcontroladores - ARM

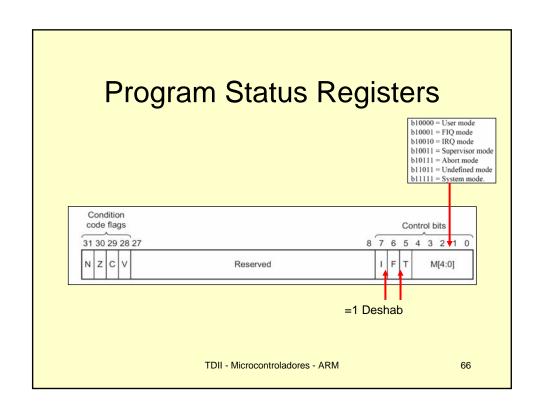

#### **REGISTROS ARM7.**

- R15: contador de programa

- R16: registro de estado ( CPSR, Current Program Status Register )

- SPSR: Saved Program Status Register

TDII - Microcontroladores - ARM

35

Arquitectura FIQ IRQ Undef Abort User гO r1 User 12 mode г3 r0-r7, User User User User r4 r15, Thumb state mode mode mode mode 15 and Low registers r0-r12, r0-r12, r0-r12, r0-r12, rβ cpsr r15, r15, r15, r15, r7 and and and and 18 18 cpsr cpsr cpsr cpsr ۴9 r10 Thumb state r10 High registers r11 r11 r12 r12 r13 (sp) r14 (Tr) r13 (sp) r14 (Tr) r13 (sp) r14 (Tr) r13 (sp) r13 (sp) r13 (sp) r14 (Ir) r14 (Ir) r14 (Tr) r15 (pc) cpsr spsr spsr Note: System mode uses the User mode register set

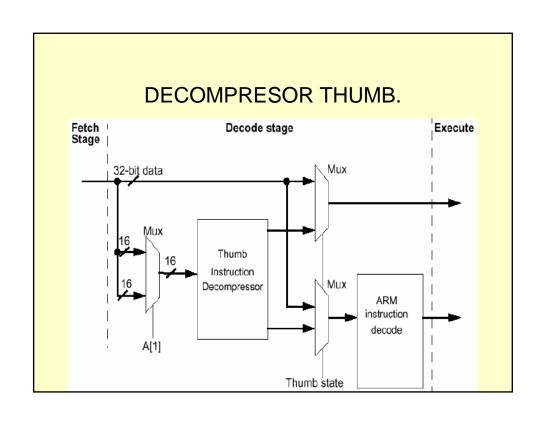

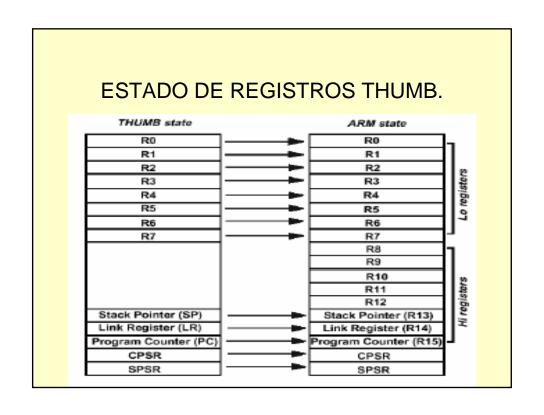

#### ARM vs. Thumb

#### ARM

- Instrucciones fijas de 32bit

- Instrucciones simples pueden realizar más funciones que una THUMB.

- Identical execution speed compared to THUMB from Flash/EE ( CD > 0 ) and SRAM ( CD >= 0 )

- La tabla de vectores en ARM

#### THUMB

- Instrucciones fijas de 16bits

- Aumentan la densidad de código

- Aumentan la velocidad de ejecución

- Repertorio de instrucciones sencillo

- Conmuta a modo ARM en cada excepción

- Acceso limitado al banco de registros.

TDII - Microcontroladores - ARM

37

#### Instrucciones ARM7

- Instrucciones de 32 bits en el modo de operación nativo ARM: longitud de palabra de 32 bits

- Todas las instrucciones son condicionales

- En ejecución normal (incondicional), la condición AL (always) se establece en el campo condición

- En operaciones condicionales se selecciona una de las 14 condiciones

- 36 formatos de instrucciones

TDII - Microcontroladores - ARM

39

#### Instrucciones ARM7

- 11 tipos básicos de instrucciones.

- Dos de estos tipos emplean la ALU, el desplazador en barril y el multiplicador para ejecutar operaciones a alta velocidad sobre datos en los registros.

- Ejemplos: AND, EOR, SUB, RSB, ADD, ADC, SBC, RSC, TST, TEQ, CMP, CMN, ORR, MOV, BIC, MVN, (Multiplicaciones) MUL, MLA, MULL, MLAL

TDII - Microcontroladores - ARM

| Cond | 0 | 0 | - | ( | )pc | 000 | le | S |   | Rn               | Rn Rd |    | Γ    | Operand 2            |                     |     |      |     | Data Processing /<br>PSR Transfer |    |   |     |        |                                         |

|------|---|---|---|---|-----|-----|----|---|---|------------------|-------|----|------|----------------------|---------------------|-----|------|-----|-----------------------------------|----|---|-----|--------|-----------------------------------------|

| Cond | 0 | 0 | 0 | 0 | 0   | 0   | Α  | s | Г | Rd               |       | Г  | Rr   | 1                    | T                   | F   | ₹s   |     | 1                                 | 0  | 0 | 1   | Rm     | Multiply                                |

| Cond | 0 | 0 | 0 | 0 | 1   | U   | Α  | s |   | Rdh              | fi    | Г  | Rdl  | .0                   | T                   | F   | Rη   |     | 1                                 | 0  | 0 | 1   | Rm     | Multiply Long                           |

| Cond | 0 | 0 | 0 | 1 | 0   | В   | 0  | 0 | Г | Rn               |       | Г  | Ro   | 1                    | 0                   | 0   | O    | 0   | 1                                 | 0  | 0 | 1   | Rm     | Single Data Swap                        |

| Cond | 0 | 0 | 0 | 1 | 0   | 0   | 1  | 0 | 1 | 1 1              | 1     | 1  | 1    | 1 1                  | 1                   | 1   | 1    | 1   | 0                                 | 0  | 0 | 1   | Rn     | Branch and Exchang                      |

| Cond | 0 | 0 | 0 | Р | U   | 0   | W  | L | Г | Rn               |       | Γ  | Ro   |                      | 0                   | 0   | C    | 0   | 1                                 | S  | Н | 1   | Rm     | Halfword Data Trans<br>register offset  |

| Cond | 0 | 0 | 0 | Р | U   | 1   | w  | L |   | Rn               |       |    | Ro   | i                    |                     | C   | off: | set | 1                                 | s  | Н | 1   | Offset | Halfword Data Trans<br>immediate offset |

| Cond | 0 | 1 | - | Р | U   | В   | w  | L | Г | Rn Rd Offset     |       |    |      | Single Data Transfer |                     |     |      |     |                                   |    |   |     |        |                                         |

| Cond | 0 | 1 | 1 | Г | _   |     | _  | _ |   | 1                |       |    |      |                      | Undefined           |     |      |     |                                   |    |   |     |        |                                         |

| Cond | 1 | 0 | 0 | Р | U   | S   | W  | L |   | Rn Register List |       |    |      |                      | Block Data Transfer |     |      |     |                                   |    |   |     |        |                                         |

| Cond | 1 | 0 | 1 | L | Г   |     |    |   |   |                  |       |    |      | 0                    | fse                 | t   |      |     |                                   |    |   |     |        | Branch                                  |

| Cond | 1 | 1 | 0 | Р | U   | N   | w  | L |   | Rn               |       | Γ  | CR   | d                    | Γ                   | С   | P#   | ŧ   | Γ                                 |    |   | Off | set    | Coprocessor Data<br>Transfer            |

| Cond | 1 | 1 | 1 | 0 | (   | P   | Op | ю |   | CR               | 1     |    | CR   | d                    |                     | С   | P#   | ŧ   |                                   | CF | ) | 0   | CRm    | Coprocessor Data<br>Operation           |

| Cond | 1 | 1 | 1 | 0 | CF  | P ( | рс | L |   | CR               | 1     |    | Ro   | 1                    |                     | С   | P#   | ¥   |                                   | CF | • | 1   | CRm    | Coprocessor Registe<br>Transfer         |

| Cond | 1 | 1 | 1 | 1 | Т   |     |    | _ | _ |                  |       | la | nore | d b                  | v pi                | roc | es   | sor | _                                 |    |   | _   |        | Software Interrupt                      |

TDII - Microcontroladores - ARM

41

# Repertorio de instrucciones

Todas las instrucciones son condicionales

| Code | Suffix | Flags                       | Meaning                 |

|------|--------|-----------------------------|-------------------------|

| 0000 | EQ     | Z set                       | equal                   |

| 0001 | NE     | Z clear                     | not equal               |

| 0010 | CS     | C set                       | unsigned higher or same |

| 0011 | CC     | C clear                     | unsigned lower          |

| 0100 | MI     | N set                       | negative                |

| 0101 | PL     | N clear                     | positive or zero        |

| 0110 | VS     | V set                       | overflow                |

| 0111 | VC     | V clear                     | no overflow             |

| 1000 | HI     | C set and Z clear           | unsigned higher         |

| 1001 | LS     | C clear or Z set            | unsigned lower or same  |

| 1010 | GE     | N equals V                  | greater or equal        |

| 1011 | LT     | N not equal to V            | less than               |

| 1100 | GT     | Z clear AND (N equals V)    | greater than            |

| 1101 | LE     | Z set OR (N not equal to V) | less than or equal      |

| 1110 | AL     | (ignored)                   | always                  |

TDII - Microcontroladores - ARM

42

- Aritméticas

- ADD r0,r1,r2

- ADC r0,r1,r2

- SUB r0,r1,r2

- SBC r0,r1,r2

- RSB r0,r1,r2 ;inversa

- RSB r0, r1, r2 ; r0 := r2 r1 + c 1

TDII - Microcontroladores - ARM

43

# Repertorio de instrucciones

- Aritméticas

- ADD r3,r2,#1

- ADD r3,r2,r1, Isl #3 (Isr, asl, asr, ror, rrx)

- ADD r5,r5,r3, LSL r2

- MUL r4,r3,r2

- -MLA r4,r3,r2,r1 ;r4:=(r3 x r2 + r1)

- RSB r0,r0,r0, LSL #3

- »; Multiplicar por 7

TDII - Microcontroladores - ARM

- Lógicas

- AND r0,r1,r2

- ORR r0,r1,r2

- EOR r0,r1,r2; r0:= r1 xor r2

- -BIC r0,r1,r2 ; r0:= r1 and not r2

- AND r8,r7,#&ff

TDII - Microcontroladores - ARM

45

# Solo afectan los Flags

```

CMP r1, r2 ; cc por r1 - r2

CMN r1, r2 ; cc por r1 + r2

TST r1, r2 ; cc por r1 and r2

TEQ r1, r2 ; cc por r1 xor r2

```

TDII - Microcontroladores - ARM

# Inmediatas

- ADD r3, r3,#1 ; r3 := r3 + 1

- AND r8, r7,#&ff ; r8 := r7[7:0]

TDII - Microcontroladores - ARM

47

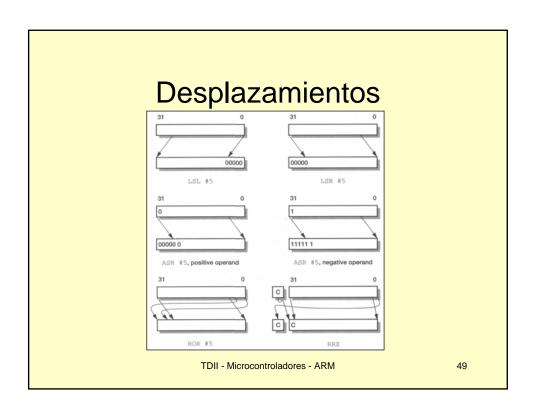

# Desplazamientos

- ADD r3, r2, r1, LSL #3; r3 := r2 + 8 x r1

- ADD r5, r5, r3, LSL r2; r5 : = r5 + r3 x  $2^{r2}$

TDII - Microcontroladores - ARM

# Modificando el CCR

```

ADDS r2, r2, r0; 32-bit carry out -> C..

ADC r3, r3, r1; .. and added into high word

```

TDII - Microcontroladores - ARM

#### Movimiento de Datos

- Movimiento

- MOV r0,r2

- -MVN r0,r2; r0:=not r2

- LDR r0,[r1]

- STR r0,[r1]

- LDR r0,[r1], #4

- LDR r0,[r1,#4]!

TDII - Microcontroladores - ARM

51

# Copia de tablas

TDII - Microcontroladores - ARM

# Pre y post indexado

```

LDR r0,[r1,#4]; r0 := men32[r1+4]

```

```

LDR r0,[r1,#4]!; r0 := mem32[r1+4]; r1 := r1+4

```

TDII - Microcontroladores - ARM

53

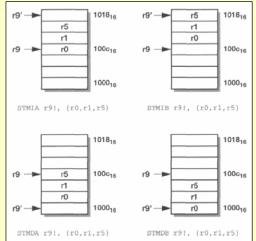

# Tablas y registros

```

LDMIA r1, \{r0,r2,r5\} ; r0 := mem_{32}[r1] ; r2 := mem_{32}[r1 + 4] ; r5 := mem_{32}[r1 + 8]

```

TDII - Microcontroladores - ARM

# Uso de la Pila

```

LDMIA r0!, {r2-r9}

STMIA r1, {r2-r9}

```

```

STMFD r13!, {r2-r9}

LDMIA r0!, {r2-r9}

STMIA r1, {r2-r9}

LDMFD r13!, {r2-r9}

```

TDII - Microcontroladores - ARM

55

# Transferencia de Registros

TDII - Microcontroladores - ARM

# Copia de bloques y stack

|           |        | Asce                                   | nding          | Descending     |                |  |

|-----------|--------|----------------------------------------|----------------|----------------|----------------|--|

|           |        | Full                                   | Empty          | Full           | Empty          |  |

| Increment | Before | STMIB<br>STMFA                         |                |                | LDMIB<br>LDMED |  |

| increment | After  |                                        | STMIA<br>STMEA | LDMIA<br>LDMFD |                |  |

| Decrement | Before | ************************************** | LDMDB<br>LDMEA | STMDB<br>STMFD |                |  |

| Decrement | After  | LDMDA<br>LDMFA                         |                |                | STMDA<br>STMED |  |

TDII - Microcontroladores - ARM

57

#### Instrucciones ARM7

- Instrucciones de salto (Branching): BX, B, BL

- BX: Branch and eXchange, salto con cambio de conjunto de instrucciones ARM < -- > Thumb

- B: salto con desplazamiento de 24 bits con signo

- BL: enlace (link) PC -> R14

- Instrucciones de transferencia de datos: LDR, STR, LDRH, STRH, LDRSB, LDRSH, LDM, STM, SWP.

TDII - Microcontroladores - ARM

# Control de flujo

|        |                  | -                                                 |

|--------|------------------|---------------------------------------------------|

| D      |                  |                                                   |

| Branch | Interpretation   | Normal uses                                       |

| B BAL  | Unconditional    | Always take this branch                           |

|        | Always           | Always take this branch                           |

| BEQ    | Equal            | Comparison equal or zero result                   |

| BNE    | Not equal        | Comparison not equal or non-zero result           |

| BPL    | Plus             | Result positive or zero                           |

| BMI    | Minus            | Result minus or negative                          |

| BCC    | Carry clear      | Arithmetic operation did not give carry-out       |

| BLO    | Lower            | Unsigned comparison gave lower                    |

| BCS    | Carry set Higher | Arithmetic operation gave carry-out               |

| BHS    | or same          | Unsigned comparison gave higher or same           |

| BVC    | Overflow clear   | Signed integer operation; no overflow occurred    |

| BVS    | Overflow set     | Signed integer operation; overflow occurred       |

| BGT    | Greater than     | Signed integer comparison gave greater than       |

| BGE    | Greater or equal | Signed integer comparison gave greater or equal   |

| BLT    | Less than        | Signed integer comparison gave less than          |

| BLE    | Less or equal    | Signed integer comparison gave less than or equal |

| BHI    | Higher           | Unsigned comparison gave higher                   |

| BLS    | Lower or same    | Unsigned comparison gave lower or same            |

|        |                  |                                                   |

TDII - Microcontroladores - ARM

59

# Ejemplo

```

CMP r0,#5

BEQ SALTO

ADD r1,r1,r0

```

SUB r1,r1,r2 ; r0:=r1 + r0 - r2

Salto:

CMP r0,#5 ADDNE r1,r1,r0

SUBNE r1,r1,r2 ;r0:=r1 + r0 - r2

TDII - Microcontroladores - ARM

# **Subrutinas**

BL subru

. . .

Subru: ....

mov pc,r14

TDII - Microcontroladores - ARM

61

#### Instrucciones ARM7

- Instrucciones de excepciones: SWI, SoftWare Interrupt.

- Instrucciones del Coprocesador: CDP, LDC, STC, MRC, MCR.

- ARM no ejecuta estas instrucciones pero deja al coprocesador la manipulación de ellas.

TDII - Microcontroladores - ARM

# Modos

| Para ejecución normal de aplicación                      |

|----------------------------------------------------------|

| Transferencia de datos de alta velocidad                 |

| Manejo general de Interrupciones                         |

| Modo protegido para el sistema operativo                 |

| Para implementar memoria virtual o protección de memoria |

| Emulación por software de coprocesadores                 |

| Para correr tareas privilegiadas del sistema operativo   |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                    |

| Registros      |                                               |  |  |  |  |  |

|----------------|-----------------------------------------------|--|--|--|--|--|

| Modo           | Indentificador de modo de bancos de registros |  |  |  |  |  |

| User           | _usrb                                         |  |  |  |  |  |

| Fast interrupt | _fiq                                          |  |  |  |  |  |

| Interrupt      | _irq                                          |  |  |  |  |  |

| Supervisor     | _svc                                          |  |  |  |  |  |

| Abort          | _abt                                          |  |  |  |  |  |

| System         | _usr                                          |  |  |  |  |  |

| Undefined      | _und                                          |  |  |  |  |  |

| TDII - Microco | ntroladores - ARM 65                          |  |  |  |  |  |

# Little endian data format

| 31 24               | 23 16                  | 15 8                | 7 0                 | -                 |

|---------------------|------------------------|---------------------|---------------------|-------------------|

| Byte 3 at address F | Byte 2 at<br>address E | Byte 1 at address D | Byte 0 at address C | Word at address C |

| Halfword 1          | at address E           | Halfword 0 a        | at address C        |                   |

| Byte 3 at address B | Byte 2 at address A    | Byte 1 at address 9 | Byte 0 at address 8 | Word at address 8 |

| Halfword 1          | at address A           | Halfword 0          | at address 8        | -                 |

| Byte 3 at address 7 | Byte 2 at address 6    | Byte 1 at address 5 | Byte 0 at address 4 | Word at address 4 |

| Halfword 1          | at address 6           | Halfword 0          | at address 4        | -                 |

| Byte 3 at address 3 | Byte 2 at address 2    | Byte 1 at address 1 | Byte 0 at address 0 | Word at address 0 |

| Halfword 1          | at address 2           | Halfword 0          | at address 0        | -                 |

TDII - Microcontroladores - ARM

# Big Endian data format

| 31 24                  | 23 16                  | 15 8                | 7 0                    |                   |

|------------------------|------------------------|---------------------|------------------------|-------------------|

| Byte 0 at<br>address F | Byte 1 at<br>address E | Byte 2 at address D | Byte 3 at<br>address C | Word at address C |

| Halfword 0             | at address E           | Halfword 1 a        | at address C           |                   |

| Byte 0 at address B    | Byte 1 at address A    | Byte 2 at address 9 | Byte 3 at address 8    | Word at address 8 |

| Halfword 0             | at address A           | Halfword 1          | at address 8           |                   |

| Byte 0 at address 7    | Byte 1 at address 6    | Byte 2 at address 5 | Byte 3 at address 4    | Word at address 4 |

| Halfword 0             | at address 6           | Halfword 1          | at address 4           |                   |

| Byte 0 at address 3    | Byte 1 at address 2    | Byte 2 at address 1 | Byte 3 at address 0    | Word at address 0 |

| Halfword 0             | at address 2           | Halfword 1          | at address 0           |                   |

TDII - Microcontroladores - ARM

# Excepciones

- Dir Prox Instrucción → LR

- Si la excepción ocurre en estado ARM, PC+4 ó PC+8

- Si la excepción ocurre en Thumb PC+2 ó PC+4

- Copia CPSR al correspondiente SPSR

- Fuerza los bits de modo del CPSR (según la excepción

- Fuerza a buscar con el PC la instrucción según el vector

TDII - Microcontroladores - ARM

69

# Retorno de excepciones

|                       | Saved  | LR value | B                              |                                                     |  |  |

|-----------------------|--------|----------|--------------------------------|-----------------------------------------------------|--|--|

| Exception             | ARM    | Thumb    | Recommended return instruction | Return point                                        |  |  |

| Reset                 | -      | -        | -                              | After Reset, r14_svc value is Unpredictable.        |  |  |

| Data Abort            | PC + 8 | PC + 8   | SUBS PC, R14_abt, #8           | Returns to aborted instruction.                     |  |  |

| FIQ                   | PC + 4 | PC + 4   | SUBS PC, R14_fiq, #4           | Returns to interrupted instruction.                 |  |  |

| IRQ                   | PC + 4 | PC + 4   | SUBS PC, R14_irq, #4           | Returns to interrupted instruction.                 |  |  |

| Prefetch Abort        | PC + 4 | PC + 4   | SUBS PC, R14_abt, #4           | Returns to aborted instruction.                     |  |  |

| Undefined instruction | PC + 4 | PC + 2   | MOVS PC, R14_und               | Returns to instruction after Undefined instruction. |  |  |

| SWI<br>instruction    | PC + 4 | PC + 2   | MOVS PC, R14_svc               | Returns to instruction after SWI instruction.       |  |  |

- CPSR ← SPSR

- Limpia Interrupt Disable

TDII Microcontroladores ARM

# Vectores de excepción

| Address    | Exception             | Mode on entry | I state on entry | F state on entry |

|------------|-----------------------|---------------|------------------|------------------|

| 0×00000000 | Reset                 | Supervisor    | Set              | Set              |

| 0×00000004 | Undefined Instruction | Undefined     | Set              | Unchanged        |

| 0×00000008 | SWI                   | Supervisor    | Set              | Unchanged        |

| 0x0000000C | Prefetch Abort        | Abort         | Set              | Unchanged        |

| 0×00000010 | Data Abort            | Abort         | Set              | Unchanged        |

| 0x00000014 | Reserved              | Reserved      | -                | -                |

| 0×00000018 | IRQ                   | IRQ           | Set              | Unchanged        |

| 0x0000001C | FIQ                   | FIQ           | Set              | Set              |

TDII - Microcontroladores - ARM

71

# Prioridades de las excepciones

| Priority | Exception                     |

|----------|-------------------------------|

| Highest  | Reset                         |

|          | Data Abort                    |

|          | FIQ                           |

|          | IRQ                           |

|          | Prefetch Abort                |

| Lowest   | Undefined Instruction and SWI |

TDII - Microcontroladores - ARM

- Para sistemas que requieren manejo completo de memoria virtual y espacios de ejecución protegidos.

- Memoria caché de 8K

- MMU: unidad controladora de memoria.

- Para aplicaciones de plataforma abierta como Windows CE, Linux, Palm OS y Symbian OS.

TDII - Microcontroladores - ARM

73

# Big Endian data format

|                                                 | <u> </u>               |                        |                     |                   |

|-------------------------------------------------|------------------------|------------------------|---------------------|-------------------|

| 31 24                                           | 23 16                  | 15 8                   | 7 0                 | _                 |

| Byte 0 at address F                             | Byte 1 at<br>address E | Byte 2 at address D    | Byte 3 at address C | Word at address C |

| Halfword 0                                      | at address E           | Halfword 1 a           | at address C        | _                 |

| Byte 0 at address B                             | Byte 1 at address A    | Byte 2 at<br>address 9 | Byte 3 at address 8 | Word at address 8 |

| Halfword 0 at address A Halfword 1 at address 8 |                        |                        |                     |                   |

| Byte 0 at address 7                             | Byte 1 at address 6    | Byte 2 at address 5    | Byte 3 at address 4 | Word at address 4 |

| Halfword 0                                      |                        |                        |                     |                   |

| Byte 0 at address 3                             | Byte 1 at address 2    | Byte 2 at address 1    | Byte 3 at address 0 | Word at address 0 |

| Halfword 0                                      | at address 2           | Halfword 1             | at address 0        | -                 |

TDII - Microcontroladores - ARM

## Excepciones

- Dir Prox Instrucción → LR

- Si la excepción ocurre en estado ARM, PC+4 ó PC+8

- Si la excepción ocurre en Thumb PC+2 ó PC+4

- Copia CPSR al correspondiente SPSR

- Fuerza los bits de modo del CPSR (según la excepción

- Fuerza a buscar con el PC la instrucción según el vector

TDII - Microcontroladores - ARM

75

# Retorno de excepciones

|                       | Saved LR value |        | Recommended          |                                                     |  |

|-----------------------|----------------|--------|----------------------|-----------------------------------------------------|--|

| Exception             | ARM            | Thumb  | return instruction   | Return point                                        |  |

| Reset                 | -              | -      | -                    | After Reset, r14_svc value is Unpredictable.        |  |

| Data Abort            | PC + 8         | PC + 8 | SUBS PC, R14_abt, #8 | Returns to aborted instruction.                     |  |

| FIQ                   | PC + 4         | PC + 4 | SUBS PC, R14_fiq, #4 | Returns to interrupted instruction.                 |  |

| IRQ                   | PC + 4         | PC + 4 | SUBS PC, R14_irq, #4 | Returns to interrupted instruction.                 |  |

| Prefetch Abort        | PC + 4         | PC + 4 | SUBS PC, R14_abt, #4 | Returns to aborted instruction.                     |  |

| Undefined instruction | PC + 4         | PC + 2 | MOVS PC, R14_und     | Returns to instruction after Undefined instruction. |  |

| SWI<br>instruction    | PC + 4         | PC + 2 | MOVS PC, R14_svc     | Returns to instruction after SWI instruction.       |  |

- CPSR ← SPSR

- Limpia Interrupt Disable

TDII Microcontroladores ARM

# Vectores de excepción

| Address     | Exception             | Mode on entry | I state on entry | F state on entry |

|-------------|-----------------------|---------------|------------------|------------------|

| 0×000000000 | Reset                 | Supervisor    | Set              | Set              |

| 0x00000004  | Undefined Instruction | Undefined     | Set              | Unchanged        |

| 0×00000008  | SWI                   | Supervisor    | Set              | Unchanged        |

| 0x0000000C  | Prefetch Abort        | Abort         | Set              | Unchanged        |

| 0x00000010  | Data Abort            | Abort         | Set              | Unchanged        |

| 0x00000014  | Reserved              | Reserved      | -                | -                |

| 0x00000018  | IRQ                   | IRQ           | Set              | Unchanged        |

| 0x0000001C  | FIQ                   | FIQ           | Set              | Set              |

TDII - Microcontroladores - ARM

77

# Prioridades de las excepciones

| Priority | Exception                     |  |

|----------|-------------------------------|--|

| Highest  | Reset                         |  |

|          | Data Abort                    |  |

|          | FIQ                           |  |

|          | IRQ                           |  |

|          | Prefetch Abort                |  |

| Lowest   | Undefined Instruction and SWI |  |

TDII - Microcontroladores - ARM

- Para sistemas que requieren manejo completo de memoria virtual y espacios de ejecución protegidos.

- Memoria caché de 8K

- MMU: unidad controladora de memoria.

- Para aplicaciones de plataforma abierta como Windows CE, Linux, Palm OS y Symbian OS.

TDII - Microcontroladores - ARM

79

## Repertorio de instrucciones

- Comparación

- CMP r1,r2

- CMN r1,r2

- TST r1,r2

- TEQ r1,r2

TDII - Microcontroladores - ARM

#### Instrucciones de Movimiento

- MOV r0,r2

- -MVN r0,r2; r0:=not r2

- LDR r0,[r1]

- STR r0,[r1]

- LDR r0,[r1], #4

- LDR r0,[r1,#4]!

TDII - Microcontroladores - ARM

#### Aritméticas

- ADD r1, r2, r3 ; r1 = r2 + r3

- ADC r1, r2, r3 ; r1 = r2 + r3 + C

- SUB r1, r2, r3 ; r1 = r2 r3

- SUBC r1, r2, r3 ; r1 = r2 r3 + C 1

- RSB r1, r2, r3 ; r1 = r3 r2

- RSC r1, r2, r3 ; r1 = r3 r2 + C 1

TDII - Microcontroladores - ARM

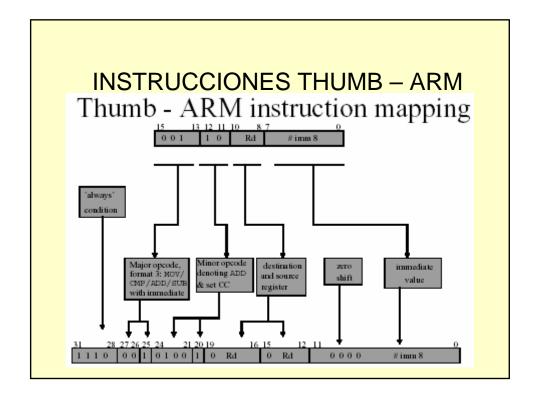

# CONJUNTO DE INSTRUCCIONES THUMB.

- La longitud de palabra se reduce a 16 bits.

- Las instrucciones siguen su propia sintaxis, pero cada instrucción tiene su contraparte en ARM nativo.

- Debido a la reducción de bits, se pierde cierta funcionalidad.

- Existen 19 formatos diferentes de instrucción Thumb.

TDII - Microcontroladores - ARM

# SUMARIO: CONJUNTO DE INSTRUCCIONES THUMB.

| Mi | nemonic | Operation               | Mnemonic | Operation                    |

|----|---------|-------------------------|----------|------------------------------|

| M  | OV      | Move                    | MVN      | Move Not                     |

| A[ | DD D    | Add                     | ADC      | Add with Carry               |

| SI | JB      | Subtract                | SBC      | Subtract with Carry          |

| R  | SB      | Reverse Subtract        | RSC      | Reverse Subtract with Carry  |

| Cf | ИP      | Compare                 | CMN      | Compare Negated              |

| TS | šΤ      | Test                    | NEG      | Negate                       |

| 1A | ND      | Logical AND             | BIC      | Bit Clear                    |

| EC | OR      | Logical Exclusive OR    | ORR      | Logical (inclusive) OR       |

| LS | SL .    | Logical Shift Left      | LSR      | Logical Shift Right          |

| AS | SR      | Arithmetic Shift Right  | ROR      | Rotate Right                 |

| M  | JL      | Multiply                | BKPT     | Breakpoint                   |

| В  |         | Unconditional Branch    | Bcc      | Conditional Branch           |

| BL |         | Branch and Link         | BLX      | Branch and Link and Exchange |

| B) | (       | Branch and Exchange     | SWI      | Software Interrupt           |

| LD | R .     | Load Word               | STR      | Store Word                   |

| LD | )RH     | Load Halfword           | STRH     | Store Halfword               |

| LD | )RB     | Load Byte               | STRB     | Store Byte                   |

| LD | RSH)    | Load Signed Halfword    | LDRSB    | Load Signed Byte             |

| LD | MIA     | Load Multiple           | STMIA    | Store Multiple               |

| Pl | JSH     | Push Registers to stack | POP      | Pop Registers from stack     |

#### APLICACIONES DE THUMB.

- Para optimizar el costo y el consumo de potencia.

- Para rutinas de control largas y no críticas.

TDII - Microcontroladores - ARM

Autor Marcelo Romeo UTN-FRBA Archivo I2C\_Master.c ADuC7026. Hardware Descripcion I2C master para conectarse con Dispositivo externo esclavo Opera en dos modos, lectura y escritura (recibe y transmite Al inicio de la transmisión I2C el Master envía la dirección. El LSB indica si el Master realizará lectura (1) o escritura (0). #include<ADuC7026.h> #define count 0x4: // Número de bytes a ser recibidos - 1 void delay(int); void IRQ\_Handler() \_\_irq; int i = 0, dat[5]; // El tamaño de dat deberá ser (count + 1) TDII - Microcontroladores - ARM

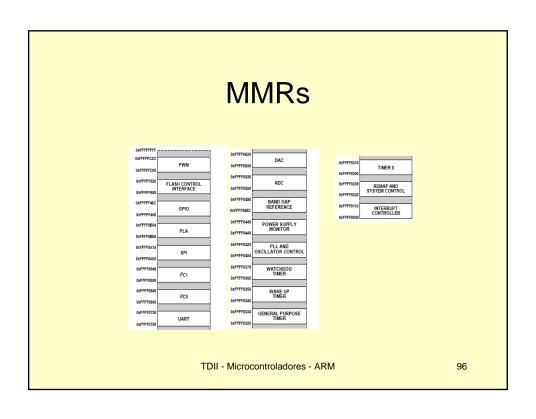

#### **IRQEN**

| IRQEN Re | gister     |               |        |

|----------|------------|---------------|--------|

| Name     | Address    | Default Value | Access |

| IRQEN    | 0xFFFF0008 | 0x00000000    | R/W    |

|          |            |               | 40     |

0 All interrupts OR'ed 1 SWI: not used in IRQEN/CLR and FIQEN/CLR 2 Timer 0 3 Timer 1

4 Wake Up timer – Timer 2 5 Watchdog timer – Timer 3 6 Flash control 7 ADC channel

8 PLL lock 9 I2C0 Slave 10 I2C0 Master 11 I2C1 Master 12 SPI Slave 13 SPI Master 14 UART

15 External IRQ0 16 Comparator 17 PSM

18 External IRQ1 19 PLA IRQ0 20 PLA IRQ1 21 External IRQ2 22 External IRQ3 23 PWM trip 24 PWM sync

TDII - Microcontroladores - ARM

- Es una familia constituida por los procesadores ARM920T, ARM922T Y ARM940T.

- Construida en base al procesador ARM9TDMI.

- Set de instrucciones de 16 Bits.

- El procesador es RISC de 32 Bits.

- Buffer de escritura de 8 entradas.

TDII - Microcontroladores - ARM

- Pipeline de 5 estados que alcanza 1.1 MIPS/MHz, expandible a 300 MIPS.

- Bus de interface AMBA de 32 Bits.

- MMU (Memory Management Unit) que soporta Windows CE, Symbian OS, Linux, Palm OS.

- MPU (Memory Protection Unit) soportando una amplia gama de sistemas operativos en tiempo real, incluyendo VxWORKS.

TDII - Microcontroladores - ARM

103

#### ARM920T Y ARM922T

- Macrocelulas basadas en el ARM9TDMI RISC de 32 Bits convenientes para una gama de aplicaciones basadas en plataforma OS, ofrecen caches para instrucciones y datos, son idénticos pero se diferencian en que uno es de 16k y el otro de 8k.

- MMU permitiendo soporte para otros sistemas operativos importantes.

TDII - Microcontroladores - ARM

## **APLICACIONES**

- En las próximas generaciones de Teléfonos, comunicadores y PDA'S.

- En procesadores 3G.

- En dispositivos basados en Plataforma OS.

- Cámaras digitales.

- Decodificadores de Audio y video.

- En la industria automotiva.

TDII - Microcontroladores - ARM